AMAZON multi-meters discounts AMAZON oscilloscope discounts

A free-running relaxation oscillator is actually a two-stage R-C amplifier with the output fed back to the input, forming an astable multivibrator. Operation is continuous, with one stage conducting while the other is cut off, and switching time depends on the R-C values.

Output from this type of circuit, obtained from either collector, is essentially a square wave. Synchronization is achieved by the application of positive trigger pulses, triggering a nonconductive stage just before conduction would normally occur.

An Eccles-Jordan flip-flop circuit is quite like the cross-coupled multi vibrator except it has two stable states (bistable) and can remain at rest in either one. In control circuits and computers, for example, its "one" state is X1 on, X2 off; the "zero" state is X1 off, X2 on. A pulse input is often applied to X1 as the clearing or reset pulse to assure the off, or "zero," state at the start.

A negative pulse switches the state, causing a neon lamp to light; this is the "one" state. After another pulse, the state is again reversed and the lamp goes out. Because this two-stage device requires two trigger pulses to restore its original state, it is known as a count-by-two circuit.

Another circuit variation is the monostable multivibrator, which has only one stable state. When triggered into its other state, it will automatically return to its primary, or stable, state.

This type of circuit is also known as a one-shot multivibrator.

NONSATURATED FLIP-FLOP

There are two major types of flip-Hops-saturated and non saturated. When the stages are switched from cutoff to saturation, it is a saturated circuit. Such circuits are slower in operation ( lower in frequency) than non-saturated circuits because of the storage time of minority carriers. On the other hand, a saturated flip-Hop can switch more current.

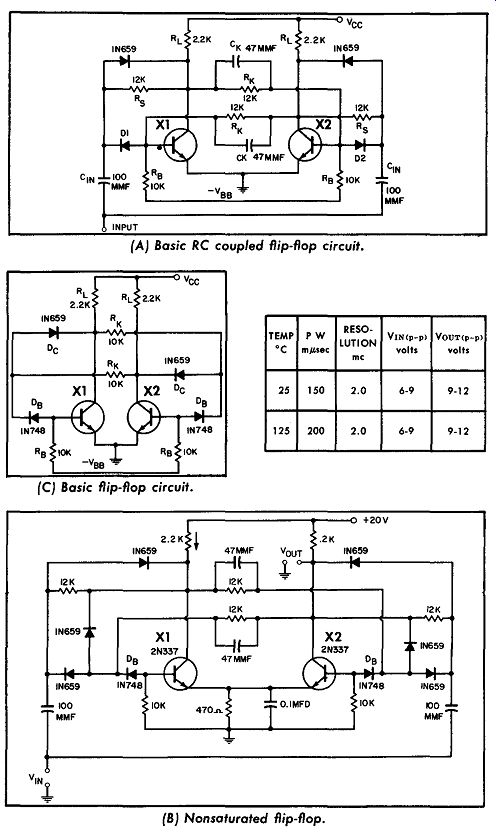

------------ Non-saturated flip-flop. (C) Basic flip-flop circuit. (B) Non-saturated

flip-flop. (A) Basic RC coupled flip-flop circuit.

To permit pulses from a single source to trigger either transistor, steering circuits are used. The 1N659 diodes and resistors Rs form the steering circuits in circuit A. Capacitors CK are used to speed up circuit action. The diodes connected across Rs are used so that the circuit will respond at the maximum repetition rate. If a number of flip-flops are cascaded to form a binary counter, only the first stage, and possibly the second, need these diodes.

Negative base triggering is used for all flip-flops; for NPN transistors, negative pulses applied to the base turn an "on" transistor off. A flip-flop usually drives a number of circuits; therefore, its output must be sufficient to handle a fairly heavy load. When flip-flops are cascaded, the output voltage or current must be sufficient to trigger the next stage. The input-pulse width and amplitude are also important and will usually determine the input and cross-coupling capacitor values.

One technique for designing a non-saturated flip-flop is to hold the transistors out of saturation with reference and clamping diodes. This technique is illustrated in circuit B, where diodes have been added to the basic circuit. During the time a transistor is on, diode DC clamps the collector voltage above the base voltage by the reference voltage of DB, thus keeping the transistor out of saturation. DB passes more than enough current to control the collector current and voltage. When the transistor is off, De does not conduct and DB still maintains a reference voltage but now passes only a very small current.

Test results of circuit B are shown in the chart. PW is the pulse width of the input measured at the 10% amplitude level; resolution is the maximum rate of the input pulses for a full output voltage.

Coupling capacitors, input capacitors, and steering circuits may be added to circuit C. This is essentially what has been done in circuit C; however, the input steering diode connects to the junction of De and DB rather than to the base of the transistor, thus permitting smaller trigger voltages to be used.

MONOSTABLE MULTIVIBRATORS

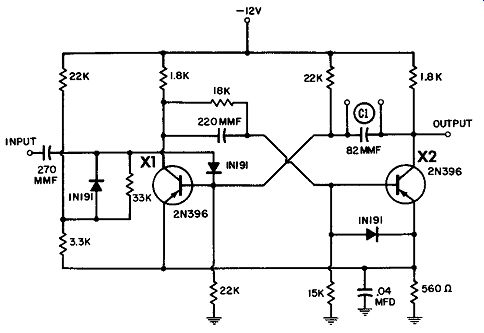

Both circuits shown here have only one stable state. When triggered, each circuit switches to the unstable state. This state is achieved by using cross-coupling between stages. Because of the time constants used, the circuit remains in the unstable state for a predetermined length of time, after which it reverts to its stable state. Because of this action, these circuits are useful as pulse standardizers.

------------ Monostable multivibrator.

Output (at collectors) has 8 volt level change.

Output pulse duration 2 µsec to 1 sec. Maximum input frequency 250 khz.

Maximum required input pulse is 5 volts.

Duty cycle exceeds 60%

Ambient temperature -56° C to 71 ° C.

(A) RC coupled.

Output at collector has 5 volt level change.

Output pulse duration approx. 600 µsec.

Maximum input pulse required 3 volts.

Ambient temperature -56° C to 71 ° C.

(B) Capacitor coupled.

SATURATED FLIP-FLOPS

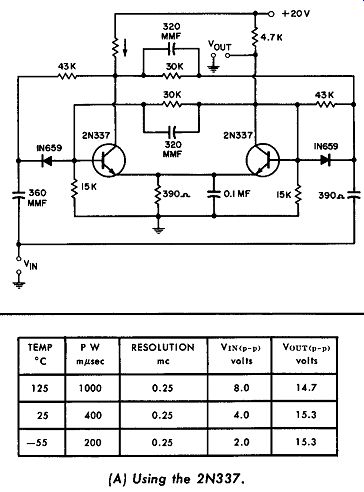

Circuit A shows the component values and temperature performance data for a saturated flip-flop using 2N337 transistors.

Only one 20-volt power supply is needed. Collector current is 3.5ma.

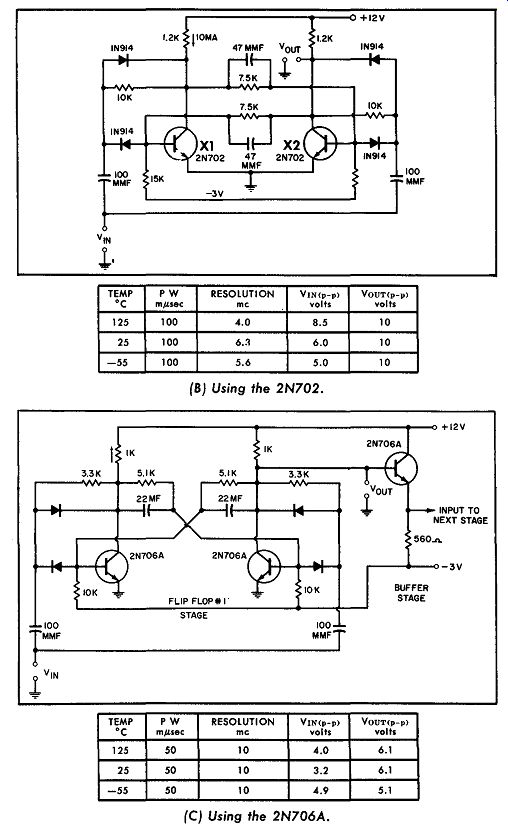

Circuit B shows the 10-ma saturated flip-Hop circuit for the 2N702 double-diffused mesa transistor. The cross coupling and input capacitors are chosen for a maximum resolution rate at an output-to-input ratio greater than 1.0. V_out has a voltage swing of 10 volts, and two power supplies are used.

Circuit C demonstrates the advantages of low-storage-time mesa transistors. Two power supplies are used to operate the 2N706A at a collector current of 10 ma. Reliable operation at 10 mhz is obtained over the temperature range of -55°C. to +125°C. (V_IN less than V_out), driving another flip-flop through a buffer stage.

------------- (A) Using the 2N337.

------------- Saturated flip-flop. (B)Using the 2N702. (C) Using the 2N706A.

DIRECT-COUPLED FLIP-FLOP

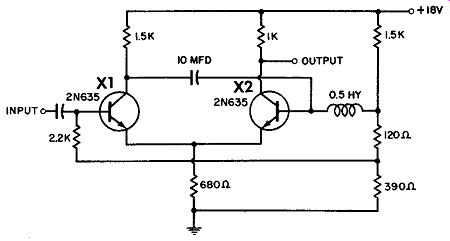

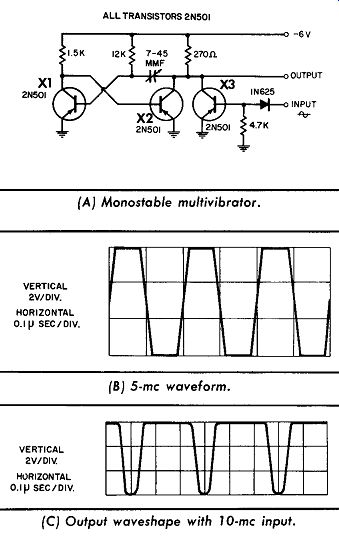

This circuit illustrates a monostable flip-flop multivibrator that can be triggered with a sine-wave input. The rise time of the output pulse is less than 18 microseconds. Output-pulse width is determined by the setting of the variable capacitor.

------- Direct coupled flip-flop.

(A) Monostable multivibrator.

(B) 5-mhz waveform.

(C) Output waveshape with 10-mhz input.

Output-pulse widths of less than 100 microseconds were obtained with a standard input pulse generator ( or a sine-wave generator operating above 1 mc). Drawing B illustrates the out put waveshape at 5 mhz. A stable scale-of-3 counter has been achieved by feeding in a sine wave from 9 to 12 mhz and adjusting the capacitor for a value of 30 mmf. The output waveshape in drawing C was obtained with a 10-mhz input.

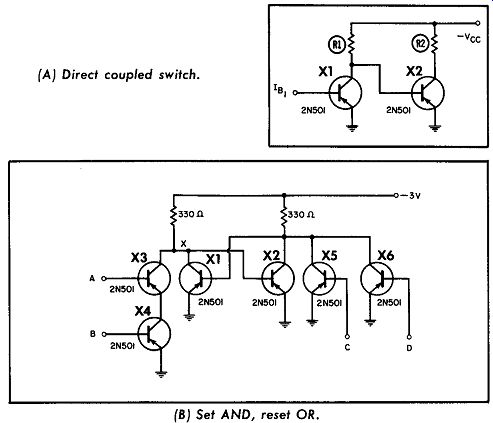

----------- (A) Direct coupled switch. (B)Set AND, reset OR. Direct coupled

transistor logic flip-flop.

This circuit was found to be insensitive to supply-voltage variations ranging from -2 to -8 volts, and to temperatures up to 65°C. The same circuit, when triggered from a continuous sine wave of 4 to 6 me, was found to count down by a scale of 2. One of its frequent applications is in computer systems requiring a countdown of pulse-generator repetition rates.

DIRECT-COUPLED TRANSISTOR LOGIC FLIP-FLOP

These figures show direct-coupled transistor logic circuits, which offer simplicity and the full use of transistor characteristics. No interstage coupling networks are needed because of the low saturation voltage of the 2N501. The main requirement of a DCTL configuration is that the saturation voltage of the transistor, applied to the base of the second stage, drop to the cutoff level. Circuit A is a two-stage direct-coupled switch. The collector of X1 is coupled directly to the base of X2. In the quiescent state, X2 will be on (conducting) and X1 will be off (nonconducting). Upon application of sufficient base current ( 1B), the collector voltage of X1 will reach a saturation level of less than .05 volt.

This voltage is low enough to turn off X2.

If the output of X2 is coupled directly to the input of X1, a binary stage is formed. As shown in Part B, the DCTL flip-flop is set by an inverted AND gate (X3-X4) and reset by an inverted OR gate (X5-X6). Assume X1 is off at the outset. X2 is then in an "on" state. If signals are present at A and B simultaneously, X3 and X4 will conduct, causing the voltage at point X to fall below .05 volt. This will turn off X2 and supply a base current to X1 which will turn it on, maintaining point X at less than .05 volt. The flip-flop is now said to be set. In order to reset the flip-flop and change the state, an input must be supplied at C or D.

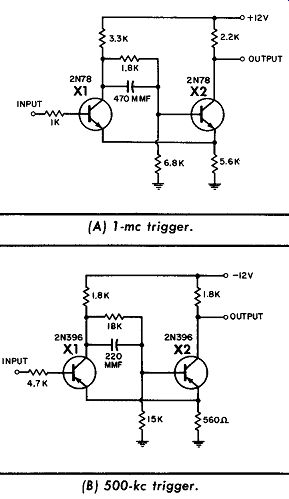

------------- Schmitt triggers. (A) 1-mhz trigger. (B) 500-khz trigger.

SCHMITT TRIGGERS

The Schmitt trigger is a bistable R-C amplifier. In circuit A, when X1 is not conducting, the voltage at the base of X2 will be about 6.8 volts because of the three-resistor voltage divider between the +12-volt source and ground. The emitter voltages of both stages are less than 6.6 volts. Thus, conduction will occur when the base is greater than 6.8 volts; X2 will conduct when the input signal is less than 5.2 volts. When the input voltage rises above this value, X1 starts conducting and X2 is cut off. When the input level drops to less than 5.2 volts, X1 goes into cutoff and X2 again conducts. This circuit operates efficiently at frequencies up to 1 me, and provides an output of at least 2 volts.

The circuit in B operates up to 500 khz. X1 conducts with an input of -5 volts or greater, and X2 conducts when the input is more positive than -2 volts. The output always has a minimum-level change of 8 volts.

FREE-RUNNING (ASTABLE) MULTIVIBRATOR

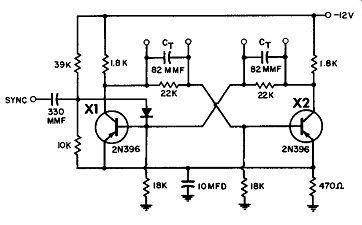

The free-running, or astable, multivibrator shown here has a frequency range from 1 hz to 250 khz, depending on the value of CT. Synchronization at a specific frequency can be achieved by using sync pulses having .an amplitude greater than 1.5 volts.

The output has at least an 8-volt swing .

------------ Free-running (astable) multivibrator.

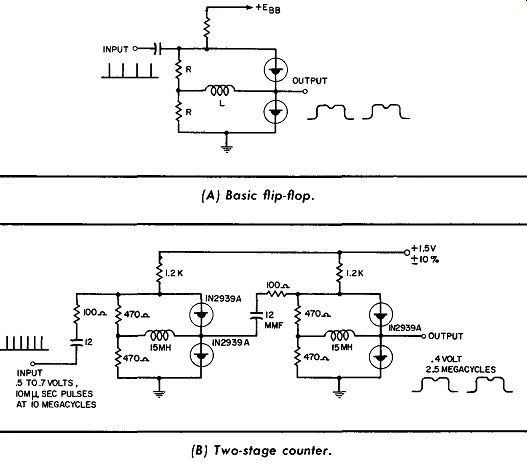

TUNNEL-DIODE FLIP-FLOP

A tunnel-diode flip-flop which requires a trigger pulse of only one polarity is shown here. The supply voltage is of a value that will permit only one tunnel diode to be in the high-voltage state.

The difference between the two tunnel-diode currents flows through the inductance.

--------- (A) Basic flip-flop. (B) Two-stage counter.

A positive trigger pulse causes the diode in the low-voltage state to switch to a high-voltage state. This action decreases the current through the inductance, resulting in the development of an induced voltage which changes through it. This voltage is of a polarity which changes the other tunnel diode to its low-voltage state. A pair of trigger pulses is required to complete one switching cycle.

The basic flip-flop circuit can be interconnected to form a counter, as in Part B. With the values of components and input pulses indicated, this counter will operate successfully up to 10 me.

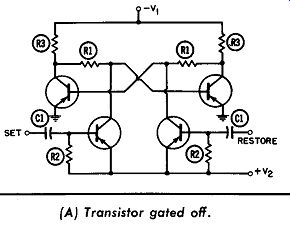

----------- (A) Transistor gated off.

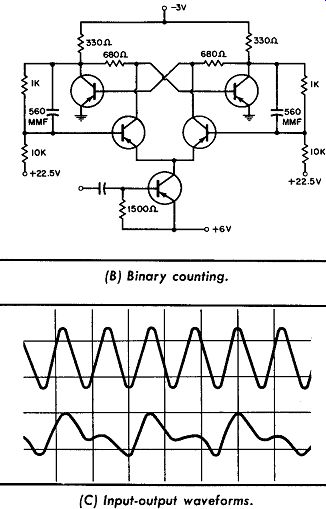

--------------- (B)Binary counting. (C) Input-output waveforms. SBT saturating

flip-flops.

SBT SATURATING FLIP-FLOPS

Here's a circuit which utilizes gating to turn the transistor off instead of on. With the proper value of V2, the gate not only turns off the conducting transistor, but also supplies current to the load resistor of the nonconducting transistor in an amount the transistor itself provides when restored to its conductive state. This pseudo-collector current reduces the delay which normally pre cedes the turn-on transient. Both turn-off and turn-on delay are thus minimized so that an entire flip-flop transition, from the time the trigger pulse is applied to the end of the switching transient, can occur within 20 microseconds when an SB-100 surface-barrier transistor ( SBT) is used.

Circuit B shows a modification which can be used for a method of binary counting. The memory voltages for steering trigger pulses to the proper gate are provided by the 1,000-ohm resistors.

These resistors, tied back to the 22.5-volt supplies through 10,000 ohm resistors, also prevent forward biasing of the collector diodes of the gates. Using SB-100 transistors, the circuit counts sine wave inputs up to 55 mhz. This circuit has operated satisfactorily up to 70 mhz with 2N501 micro-alloy diffused-base transistors (MADT). Waveform response to a 50 -mhz input for complementing base gated flip-flops is shown in Part C (vertical scale is 1 volt/ division). The input waveform appears above the output waveform.