AMAZON multi-meters discounts AMAZON oscilloscope discounts

1. ELECTRICITY AND ELECTROSTATICS DISCHARGE

1.1 Electricity and Electrostatics

In the field of electricity, electrostatics, and circuit theory, there are many discoveries and accomplishments that have lead to the foundation of the field of electrostatic discharge (ESD) phenomenon. Below is a chronological list of key events that moved the field of electrostatics forward:

_ 600 B.C. Thales of Miletus discovers electrostatic attraction.

_ 1600 A.D. William Gilbert proposes the ''electric fluid'' model.

_ 1620 A.D. Niccolo Cabeo discusses ''attractive'' and ''repulsive'' phenomena.

_ 1729 A.D. Stephen Gray demonstrates ''electricity'' can be transferred by wires.

_ 1733 A.D. Charles Francois du Fay discusses two kinds of electricity-''resinous'' and ''vitreous.''

_ 1749 A.D. Abbey Jean-Antoine Nollet invents the two-fluid model of electricity.

_ 1745 A.D. Pieter Van Musschenbroeck invents the Leyden jar, or the capacitor.

_ 1747 A.D. Benjamin Franklin proposes single fluid model, with ''positive'' and ''negative'' charge.

_ 1748 A.D. Sir William Watson develops the first ''glow discharge.''

_ 1759 A.D. Francis Ulrich Theodore Aepinus discusses ''charging by induction.''

_ 1766 A.D. Joseph Priestley deduces the electric force follows an inverse square law.

_ 1775 A.D. Henry Cavendish invents the concept of capacitance and resistance.

_ 1785 A.D. Charles Augustin Coulomb verifies the inverse square law relationship.

_ 1812 A.D. Simeon Denis Poisson demonstrates that charge resides on the surface of a conductor.

_ 1821 A.D. Humphrey Davy establishes the geometrical and thermal effects of resistance.

_ 1826 A.D. Ohm develops the relationship between potential, resistance, and current.

_ 1837 A.D. Michael Faraday discovers the concept of dielectric constants in materials.

_ 1841 A.D. James Prescott Joule shows relationship of electrical current and thermal heating.

_ 1848 A.D. Gustav Kirchhoff extends the concept of Ohm's law.

_ 1873 A.D. James Clerk Maxwell publishes the work Treatise of Electricity and Magnetism.

_ 1889 A.D. Paschen establishes a relationship explaining the electrical breakdown of gases.

_ 1906 A.D. Toepler establishes a relationship for arc resistance in a discharge process.

_ 1915 A.D. Townsend explains avalanche phenomena in materials.

1.2 Electrostatic Discharge

In the field of ESD, accomplishments to advance the field of electrostatic discharge phenomena are in the form of development of experimental discovery, analytical models, introduction of new semiconductor devices and circuits, test equipment, as well as the development of ESD standards. Below is a short chronological list of key events that moved the field of ESD:

_ 1968 A.D. D. Wunsch and R. R. Bell introduces the power-to-failure electro-thermal model in the thermal diffusion time constant regime.

_ 1970 A.D. D. Tasca develops the power-to-failure electro-thermal model in the adiabatic and steady-state time constant regime.

_ 1971 A.D. Vlasov and Sinkevitch develops a physical model for electro-thermal failure of semiconductor devices.

_ 1972 A.D. W. D. Brown evaluates semiconductor devices under high-amplitude current conditions.

_ 1981 A.D. J. Smith and W. R. Littau develops an electro-thermal model for resistors in the thermal diffusion time regime.

_ 1981 A.D. Enlow, Alexander, Pierce, and Mason addresses the statistical variation of the power-to-failure of bipolar transistors due to semiconductor manufacturing process, and ESD event variations.

_ 1983 A.D. M. Ash evaluates the non-linear nature of the power threshold and the temperature dependence of the physical parameters establishing the Ash relationship.

_ 1983 A.D. V. I. Arkihpov, E. R. Astvatsaturyan, V. I. Godovosyn, and A. I. Rudenko derives the cylindrical nature of the electro-current constriction.

_ 1985 A.D. T. J. Maloney and N. Khurana discusses transmission line pulse TLP) testing as a method for semiconductor I-V characterization and modeling.

_ 1989 A.D. Dwyer, Franklin, and Campbell extends the Wunsch-Bell model to address three-dimensional effects.

_ 1989 A.D. R. Renninger, M. Jon, D. Lin, T. Diep, and T. Welser introduces the first field induced charged device model (CDM) device simulator.

_ 1989 A.D. T. Polgreen and P. Chatterjee explain non-uniform current flow in silicided multi-finger MOSFETs.

_ 1992 A.D. M. Hargrove and S. Voldman quantify CMOS ESD networks in the first CMOS shallow trench isolation (STI) technology.

_ 1992 A.D. S. Voldman discovers the effect of MeV implanted retrograde well dose on ESD robustness.

_ 1993 A.D. D. Lin publishes the first paper on the effect of MOSFET dielectric and junction breakdown scaling on on-chip ESD protection.

_ 1993 A.D. S. Voldman publishes the first paper on the influence on MOSFET constant electric field scaling theory on ESD robustness. A ''Constant ESD scaling'' theory is developed under the constraint of maintaining ESD robustness as technology is scaled.

_ 1993 A.D. ESD Association releases the human body model (HBM) standard for semiconductor component testing.

_ 1993 A.D. H. Geiser introduces the very fast transmission line pulse (VF-TLP) ESD test system.

_ 1994 A.D. A. Ameresekera and C. Duvvury publishes on the influence of MOSFET scaling trends on ESD robustness.

_ 1994 A.D. ESD Association releases the machine model (MM) standard for semiconductor component testing.

_ 1995 A.D. A. Wallash releases the first publication on ESD failure mechanisms in magneto-resistor (MR) recording heads. The significance of the work was the first indication of ESD concerns in the magnetic recording and disk drive industry.

_ 1995 A.D. SEMATECH initiates ESD Working Group to address ESD strategic planning.

The SEMATECH effort addresses ESD technology benchmarking, ESD technology roadmap and test equipment, ESDA and JEDEC ESD specification alignment, and TLP test standard development.

_ 1996 A.D. K. Banerjee develops Ti/Al/Ti interconnect model, extending the work of D. Tasca to modern CMOS interconnects.

_ 1997 A.D. S. Voldman publishes first experimental measurements of ESD in copper (Cu) interconnects, and the comparison to aluminum (Al) interconnects. This work addressesthe influence of CMOS interconnect scaling on ESD robustness, and the evolutionary changes from aluminum to copper interconnects .

_ 1997 A.D. ESD Association Device Testing Standards Committee releases first charged device model (CDM) Standard.

_ 1997 A.D. J. Barth introduces the first commercial transmission line pulse (TLP) device simulator. The introduction of commercial systems has lead to the acceptance of the TLP methodology for ESD sensitivity testing of semiconductors.

_ 1998 A.D. SEMATECH Quality and Reliability ESD Working Group initiates transmission line pulse (TLP) standards effort.

_ 2000 A.D. S. Voldman and P. Juliano published the first ESD measurements in Silicon Germanium (SiGe) technology. The significance of this work is the beginning of the focus of ESD in radio frequency (RF) technology.

_ 2002 A.D. R. Gibson and J. Kinnear initiate the S20.20 ESD Control Certification Program. The significance of this effort is the focus on international certification of ESD control programs.

_ 2003 A.D. Oryx Instruments and Thermo KeyTek, introduces commercial very fast transmission line pulse (VF-TLP) systems. The significance of this work is the introduction of VF-TLP systems as a standard testing methodology for future ESD testing.

_ 2004 A.D. ESD Association Device Testing Standards Committee initiates the trans mission line pulse (TLP) Standard Practice document. The significance of this work is the acceptance of TLP as a standard testing methodology in the semiconductor industry.

1.3 Key ESD Patents, Inventions, and Innovations

In the field of ESD protection, there are many patents, inventions, and innovations that stimulated growth of ESD circuits as well as improved the ESD robustness of circuits themselves. ESD circuit inventions are important in providing innovations and techniques that improve the ESD robustness of semiconductor chips. Interest in ESD patenting of ESD protection networks began in the 1970s, with a continued growth in patent activity, invention, and innovations. Below is a chronological list of key innovations that moved the field of ESD protection forward in the area of ESD circuits. In some cases, no patent for the invention was pursued. Many of the patents chosen in this listing consist of the ESD design practices and subjects and topics which will be discussed in the text.

Starting from the 1970s, here is a listing of key circuit innovations and those which will be referred to in the future Sections:

_ 1970 A.D. M. Fischer (IBM). Resistor-thick oxide FET gate protection device for thin oxide FETs. IBM Technology Disclosure Bulletin 13 (5): 1272-1273. This introduced the use of a gate-coupled ''thick oxide'' field effect transistor and a series resistor element.

This invention discloses the concept of using a thick oxide insulated gate field effect transistor (IGFET) to protect a thin oxide IGFET.

_ 1971 A.D. Boss et al. (IBM). ESD network with capacitor divider and half-pass transmission gate. IBM Technology Disclosure Bulletin. This introduced the concept of using a capacitive divider across a half-pass transmission gate to reduce the gate oxide stress.

_ 1971 A.D. M. Lenzlinger (RCA). ESD distributed diode/resistor double-diode network. RCA Corporation, CD 4013. Publication: ''Gate Protection of MIS Devices'', M. Lenzlinger, IEEE Transactions on Electron Device ED-18 (4): 1971. This publication discloses the concept of a double-diode ESD network as well as a distributed diode resistor transmission line for the diode to VDD.

_ 1973 A.D. G. W. Steudel (RCA). Input transient protection for complimentary field effect transistor integrated circuit device. U.S. Patent No. 3,712,995, January 23, 1973. The patent shows a distributed double-diode ESD network with diode/resistor distributed network, but with the reverse polarity.

_ 1974 A.D. T. Enomoto and H. Morita (Mitsubishi). Semiconductor device. U.S. Patent No. 3,819,952, June 25, 1974. The patent shows the use of a first-stage gate-coupled thick oxide insulated gate field effect transistor (IGFET), a series resistor element (prior to the IGFET drain), and a IGFET source resistor element. This first stage is followed by a second-stage thin oxide IGFET whose gate is coupled to the first-stage IGFET source node. The network introduces the concept of a first- and second-stage ESD network, gate-coupling, series resistor options, as well introduces a de-biasing resistor at the source of the first stage.

_ 1979 A.D. C. Bertin (IBM). Over-voltage protective device and circuits for insulated gate transistors. U.S. Patent No. 4,139,935, February 20, 1979. This patent by Claude Bertin was the first process patent that produced a metallurgical junction with a lower break down voltage using junction ''tailoring'' where the breakdown element was to serve as a ''gate tie down'' or protection network for MOSFET gate oxides.

_ 1983 A.D. N. Sasaki (Fujitsu). Semiconductor integrated circuit device providing a protection circuit. U.S. Patent No. 4,423,431. December 27, 1983. Sasaki introduces the idea of use of a series resistor, and thin oxide transistor as a protection network. The network also introduces gate-coupled thin oxide and a resistor in series with the capacitor.

This is the first network that is using gate-coupled thin oxide devices with a resistor on the gate electrode to ground, in a single-stage implementation.

_ 1983 A.D. L. Avery (RCA). Integrated circuit protection device. U.S. Patent No. 4,400,711. August 23, 1983. This patent used a MOSFET in the regenerative feedback loop of a pnpn silicon-controlled rectifier (SCR) for ESD protection applications.

_ 1989 A.D. C. Duvvury and R. Rountree ( Texas Instruments). Output buffer with improved ESD protection. U.S. Patent No. 4,855,620, August 8, 1989. This patent is the first patent to discuss the optimization of output buffers for ESD protection improvements.

_ 1990 A.D. R. Rountree ( Texas Instruments). Circuit structure with enhanced electrostatic discharge protection. U.S. Patent No. 4,939,616, July 3, 1990. This patent discusses the formation of a low-voltage trigger pnpn silicon-controlled rectifier (SCR) using an n+ diffusion that extends outside of the n-well region to form a lower breakdown voltage and lateral npn element. This innovation was important to produce low-voltage trigger SCRs as technology began to scale.

_ 1992 A.D. A. Graham (Gazelle). Structure for providing electrostatic discharge protection. U.S. Patent No. 5,124,877, June 23, 1992. This patent introduces the concept of a diode string as well as a ''ESD discharge reference rail.'' Today, ESD diode strings are commonly used, as well as the discharge rail concept.

_ 1993 A.D. W. Miller (National Semiconductor). Electrostatic discharge detection and clamp control circuit. U.S. Patent No. 5,255,146, October 19, 1993. This patent was the first patent RC-triggered ESD power clamp network to address the presence of ''detection circuits'' which respond to the ESD pulse. This is the first patent that addresses the usage of an RC network which is chosen to be responsive to the ESD pulse network.

_ 1993 A.D. R. Merrill (National Semiconductor). Electrostatic discharge protection for integrated circuits. U.S. Patent No. 5,239,440, August 24, 1993. This innovation utilized the RC-discriminator network, inverter logic, and logic circuitry that is parallel to the pre drive circuitry, and turns on the I/O off-chip driver (OCD) output stage during ESD events.

_ 1993 A.D. Kirsch, G. Gerosa, and S. Voldman (Motorola and IBM). Snubber-clamped ESD diode string network. This network introduced a diode string as a mixed-voltage interface network and solved the reverse-Darlington amplification using a ''Snubber'' diode element. Implemented into the PowerPC microprocessor and embedded controller family. This was applied to advanced microprocessors for mixed-voltage applications.

_ 1994 A.D. D. Puar (Cirrus Logic). Shunt circuit for electrostatic discharge protection. U.S. Patent No. 5,287,241, February 15, 1994. This introduced the first RC-triggered p-channel MOSFET-based ESD power clamp network.

_ 1994 A.D. J. Pianka (AT&T). ESD protection of output buffers. U.S. Patent No. 5,345,357, September 6, 1994. Development of RC-trigger and gate coupling circuit elements for activation of the output of an n-channel MOSFET pull-up and pull-down off chip driver (OCD). This ESD technique is especially valuable for small computer system interface (SCSI) chips, since only n-channel output transistors are used as the pull-up and pull-down elements.

_ 1996 A.D. T. J. Maloney (Intel). Electrostatic discharge protection circuits using biased and terminated PNP transistor chains. U.S. Patent No. 5,530,612, June 25, 1996.

Maloney's patent application was a second ESD circuit application to address the leakage amplification in diode string ESD networks. This was applied to advanced microprocessors for mixed-voltage applications.

_ 1997 A.D. S. Voldman, S. Geissler, and E. Nowak (IBM). Semiconductor diode with silicide films and trench isolation. U.S. Patent No. 5,629,544, May 13, 1997. This is the first patent that addresses four items: first, it addresses ESD diode structures constructed in shallow trench isolation; second, it addresses STI pull-down effects; it addresses the lateral polysilicon-bound gated ESD p-n diodes; and fourth, the silicon-on-insulator (SOI) lateral ESD gated diode structures.

_ 1997 A.D. D. Krakauer, K. Mistry, S. Butler, and H. Partovi, (Digital Corp). Self referencing modulation circuit for CMOS integrated circuit electrostatic discharge protection clamps. U.S. Patent No. 5,617,283, April 1, 1997. This was the first ESD application using MOSFETs to establish a MOSFET gate-modulation network. This was applied to microprocessor applications.

_ 1997 A.D. S. Voldman (IBM). Power sequence-independent electrostatic discharge protection circuits. U.S. Patent No. 5,610,791, March 11, 1997. This patent is the first patent to address sequencing issues in a multiple-rail power supply chip. The ESD protection circuitry is power sequence-independent thereby eliminating any restrictions on the sequencing of power as applied to, and removed from, the different power supply rails of the IC chip.

_ 1997 A.D. S. Voldman (IBM). Voltage regulator bypass circuit. U.S. Patent No. 5,625,280, April 29, 1997. This patent was the first to address ESD implementations for ESD protection of voltage regulators which are integrated between peripheral I/O and core power rails. This was important for DRAM, SRAM, and ASIC applications with core regulation, mixed-voltage power, and low-voltage core voltages.

_ 1998 A.D. F. Assaderaghi, L. Hsu, J. Mandelman, G. Shahidi, and S. Voldman (IBM).

Silicon-on-insulator body-coupled gated diode for electrostatic discharge (ESD) and analog applications. U.S. Patent No. 5,811,857, September 22, 1998. This invention discusses the first body- and gate-coupled silicon on insulator (SOI) ESD network applying dynamic threshold MOS (DTMOS) concepts to ESD networks.

_ 1999 A.D. J. Chen, L. Li, T. Vrotsos, and C. Duvvury. PNP-driven NMOS ESD protection circuits. U.S. Patent No. 5,982,217, November 9, 1999. This circuit innovation uses a pnp element to improve the ESD robustness of a MOSFET ESD device. The emitter of a pnp transistor and the drain of protection NMOS device are connected to an I/O pad. The collector of the pnp transistor and the gate of the protection NMOS transistor are connected to ground through a resistor.

_ 1999 A.D. S. Voldman (IBM). Modified keeper half-latch receiver circuit. U.S. Patent No. 5,894,230, April 13, 1999. This patent addressed ESD issues with CMOS receiver circuits which utilized p-channel MOSFET feedback networks, which demonstrated ESD problems in VDD reference test modes. This was very important in achieving ESD robustness in receiver networks for applications below 0.5-mm CMOS technologies.

This network was implemented into CMOS microprocessors, CMOS logic, memory, and ASIC applications.

_ 1999 A.D. S. Voldman (IBM). Electrostatic discharge protection circuits for mixed voltage interface and multi-rail disconnected power grid applications. U.S. Patent No. 5,945,713, August 31, 1999. This patent addresses two concepts: the first concept is for an ESD diode network for a multiple power supplies and separated ground rails, as well as a second circuit is a self-bias well sequence-independent input node ESD circuit. The first network was integrated into CMOS DRAM designs, and the second ESD network was implemented into both CMOS microprocessors, servers, and ASIC I/O libraries. The self bias well sequence-independent circuit was implemented into sequence-independent I/O libraries, which required the ability to lower the power supply voltage when the input pins are positive.

_ 2000 A.D. M. D. Ker (ITRI, Taiwan). Substrate-triggering electrostatic discharge protection circuit for deep-submicron integrated circuits. U.S. Patent No. 6,072,219, June 6, 2000. The patent is the first patent to address substrate triggered ESD protection networks.

_ 2000 A.D. S. Voldman and D. Hui (IBM). Switchable active clamp network. U.S. Patent No. 6,075,399, June 13, 2000. This application demonstrates the first ''active clamp'' network that is suitable for ESD protection in triple well and silicon-on-insulator (SOI) technology that utilizes body-coupling techniques.

_ 2001 A.D. R. Mashak, R. Williams, D. Hui, and S. Voldman (IBM). Active clamp network for multiple voltages. U.S. Patent No. 6,229,372, May 8, 2001. This invention is the first active clamp network used to provide active clamping and ESD protection that utilizes MOSFET body-coupling techniques in a multiple-voltage power supply environments.

_ 2002 A.D. S. Voldman and S. Ames (IBM). Modified current mirror circuit for BiCMOS applications. U.S. Patent No. 6,404,275, June 11, 2002. The invention is the first to address the problem of current mirror circuits on input pads, and develops new current mirror circuits to improve the ESD robustness.

_ 2003 A.D. M. D. Ker, K. K. Hung, and T. H. Tang (UMC). Silicon-on-insulator diodes and ESD protection circuits. U.S. Patent No. 6,649, 944, November 18, 2003. This is the first patent of an SOI ESD lateral gated diode p + /p - /n - /n+ network which uses both well implants, and removes the gate structure for improved ESD protection levels.

_ 2003 A.D. S. Voldman, A. Botula, and D. Hui. Electrostatic discharge power clamp circuit. U.S. Patent No. 6,549,061, April 15, 2003. This is the first silicon germanium (SiGe) ESD power clamp network for mixed-voltage and mixed-signal applications using high frequency, and high-breakdown SiGe HBT devices. The significance of the invention is the utilization of the natural scaling of the breakdown voltages of a SiGe HBT device.

_ 2003 A.D. S. Voldman. SOI voltage-tolerant body-coupled pass transistors. U.S. Patent No. 6,628,159, September 30, 2003. This patent is the first patent to address the ESD failure mechanisms of a SOI half-pass transmission gate (e.g., pass transistor) using body coupling techniques.

_ 2003 A.D. K. Verhaege, M. Mergens, C. Russ, J. Armer, and P. Jozwiak. Multi-finger current ballasting ESD protection circuit and interleaved ballasting for ESD sensitive circuits. U.S. Patent No. 6,583,972, June 24, 2003. This patent addresses the concept of using gate-coupling from one MOSFET finger to another in a ''domino'' fashion.

1.4 Table of ESD Defect Mechanisms

TABLE1 ESD failure mechanisms in CMOS semiconductor devices

TABLE2 ESD failure mechanisms in silicon-on-insulator (SOI) technology

TABLE3 ESD failure mechanisms of silicon, silicon germanium, and silicon germanium carbon bipolar elements

Semiconductor device and circuit failure occurs from both electro-thermal or electrical breakdown mechanisms. The ESD failure mechanisms will be a function of the technology type, semiconductor device type, the ESD event type, the polarity of the ESD event, and the grounded reference source. In TABLE1, examples of ESD failure mechanisms are shown for bulk CMOS semiconductor device elements whether used in ESD networks or circuits.

In a silicon-on-insulator (SOI) technology, ESD failure mechanisms can be significantly different than those observed in bulk CMOS. The substrate region is physically separated from the semiconductor devices using a buried oxide (BOX) region. The existence of the BOX region changes the failure modes and mechanisms significantly. TABLE2 shows SOI ESD failure mechanisms.

In TABLE3, ESD failure mechanisms in bipolar technology are shown. In bipolar technology, and in bipolar complimentary MOS (BiCMOS), the bipolar emitter base region is the most sensitive structural feature of the bipolar transistor. Low-level ESD failures typically occur in the emitter-base junction due to thermal second breakdown. Additionally, bipolar collector-to-emitter, base-to-collector, and collector-to-substrate failures can occur but at higher voltage conditions.

TABLE4 ESD failure mechanisms in Passive elements

TABLE5 ESD failures in gallium arsenide elements

Passive elements used in CMOS, RF CMOS, BiCMOS, and RF BiCMOS include base- collector junction varactors, hyper-abrupt junction varactors, metal-insulator-metal (MIM) capacitors, and inductors. Passive elements can undergo ESD failure depending on the location within the circuit or chip. Passive elements can serve as ESD elements or circuit network elements. TABLE4 shows a listing of ESD failure mechanisms.

TABLE5 shows a listing of ESD failure mechanisms in gallium arsenide products. In the table, GaAs MESFET failures are shown. GaAs failure mechanisms occur in the GaAs device, from the physical GaAs films, and the interconnect materials (e.g., AuNiGe films).

GaAs heterojunction bipolar transistors (HBT) are sensitive in the emitter-base region similar to the silicon bipolar transistor. Additionally, passive elements are also vulnerable to ESD events. Below is a list of some GaAs failure mechanisms.

ESD failures occur in structures that are needed for semiconductor chip design. TABLE6 is a summary of the failure mechanisms. ESD failure mechanisms can occur from ''no connect pads,'' floating pads, sense pads, metal bussing, programmable power pads, decoupling capacitors, and other integration elements. TABLE6 provides a list of different type of failure mechanisms that occur in a semiconductor chip.

TABLE7 shows a listing of common circuit elements in CMOS design and BiCMOS design. The listing includes off-chip drivers (OCD), receivers, phase-lock loop, active clamp networks, decoupling capacitors, and other common circuit components. These will be discussed in the text.

TABLE6 ESD failure mechanism in semiconductor chip architecture

TABLE7 ESD failure mechanisms in common circuit networks

2. FUNDAMENTAL CONCEPTS OF ESD DESIGN

2.1 Concepts of ESD Design

Fundamental concepts and objectives exist in the ESD design of semiconductor devices, circuits, and systems. The key questions to ask about ESD design are the following:

_ What is it that makes ESD design unique?

_ How is it distinct from standard circuit design practices?

Another way of stating this is--How is ESD design practices different from all other design practices? A first unique design objective is to prevent any physical element in the system from latent or permanent damage that impacts the functionality, reliability, or quality from ESD events. A corollary to this is to prevent latent or permanent damage below a desired current or voltage magnitude. This is the first objective of ESD design. What else makes ''ESD design'' unique?

Here are some of the distinctions and differences:

_ Device Response to External Events: Design of devices and circuits to respond to (and not to respond to) unique current waveforms (e.g., current magnitude and time constants) associated with external environments.

_ Alternate Current Loops: Establishment of alternative current loops or current paths which activate during high-current or high-voltage events.

_ Switches: Establishment of ''switches'' that initiate during high current or voltage events.

_ Decoupling of Current Paths: Decoupling of sensitive current paths.

_ Decoupling of Feedback Loops: Decouple of loops that initiate pinning during off condition or ESD test modes.

_ Decoupling of Power Rails: Decoupling of electrical connections to grounded references and power supplies.

_ Local and Global Distribution: Local and global distribution of electrical and thermal phenomena in devices, circuits, and systems.

_ Usage of Parasitic Elements: Utilization and avoidance of parasitic element in the design practice.

_ Buffering: Utilization of current and voltage buffering of sensitive devices, circuits, or sub-circuits.

_ Ballasting: Introduction of resistance to redistribute current within a single element or a plurality of elements.

_ Unused Sections of a Semiconductor Device, Circuit or Chip Function: Utilize ''unused'' segments of a semiconductor device for ESD protection, which was not utilized for functional applications.

_ Impedance Matching between Floating and Non-Floating Networks: Matching of conditions during testing to allow matching between networks.

_ Unconnected Structures: Addressing structures not containing electrical connections to the power grid or circuitry.

_ Utilization of ''Dummy Structures and Dummy Circuits'': Use of ''dummy structures'' as a means to provide linewidth matching.

_ Non-scalable Source: The ESD event does not scale, while the devices are scaled each technology generation.

_ Area Efficiency: Focus on area efficiency to utilize all of the physical device area for ESD protection.

2.2 Device Response to External Events

On the first issue of preventing any physical element in the system from latent or permanent damage that impacts the functionality, reliability, or quality from ESD events, there is significant misunderstanding. It is a belief of many engineers that the objective of the ESD networks is to carry all of the ESD current, as well as be the first element to undergo failure.

It is also a belief that it does not matter if the ESD structure undergoes failure. These statements are not accurate understanding of the objective of ESD design. The role of the ESD network is to increase the ESD robustness of the complete product or application. The ''failure criteria'' is based on the functional, reliability, or quality objective of the electrical component.

In ESD design, the ESD devices as well as the circuits which are to be protected can be designed to respond to (and not to respond to) unique ESD current waveforms. In standard circuit design, digital circuits are designed to switch from logic state levels, rising or falling edges. Circuits can store information or mix different logical states. ESD networks typically are designed to respond to specific ESD pulses. These networks are unique in that they address the current magnitude, frequency, polarity, and location of the ESD events. Hence, in ESD design, the ESD networks are designed and tuned to respond to the various ESD events.

In ESD design, different stages or segments of the network can also be designed to respond to different events. For example, some stages of a network can respond to human body model (HBM) and machine model (MM) events, while other segments respond to the charged device model (CDM) event. These ESD events differ in current magnitude, polarity, time constant, as well as the location of the current source. Hence, the ESD circuit is optimized to respond and address different aspects of ESD events that circuits may be subjected to. Additionally, circuits can be modified to be less sensitive to ESD events using ESD circuit techniques. As a result, the understanding of the material, device, circuit, and system physical time constants is critical in ESD design.

2.3 Alternate Current Loops

A unique issue is the establishment of alternative current loops or current paths which activate during high current or voltage events. By establishing alternative current loops, or secondary paths, the ESD current can be redirected to prevent over-voltage of sensitive circuits. In peripheral circuit design, this concept is used for overshoot and undershoot phenomenon. In peripheral circuit design, both passive and active ''clamping'' is used to eliminate over-voltage of circuit networks; this practice is most akin to the ESD methodology. As a result, in order to have an effective ESD design strategy, this current loop must respond to the ESD event and have a low impedance. A distinction from peripheral circuit methodology of clamping is the current magnitude; ESD events have significantly higher currents than the overshoot and undershoot phenomenon experienced in peripheral circuit design. Hence, the ''ESD current loop'' must achieve a similar objective, but must have lower impedance.

2.4 Switches

On the issue of establishment of ''switches'' that initiate during high current or voltage events, the uniqueness factor is that these are at time either passive or activated by the ESD event itself. A unique feature of ESD design is that it must be active during unpowered states. Whereas in peripheral circuit design, passive and active clamps are typically utilized in powered states. Hence, the ''switches'' used to sway the current into the ESD current loop are initiated passively, or are initiated by the ESD event itself. Hence, the ESD event serves as the current and voltage source to initiate the circuit. These switches lead to ''current robbing'' and the transfer of the majority of the current from the sensitive circuit to the alternative current loop. Although today there is some interest in ESD design in powered states, the majority of testing, and design practices assume an unpowered design. As a result, the ESD design must use ''switches'' or ''triggers'' that initiate passively (e.g., a diode element), or actively (e.g., a frequency-triggered ESD network). A design objective is to provide the lowest voltage trigger allowable in the application space. Hence, a key ESD design objective is to utilize low-voltage trigger elements that serve as a means to transfer the current away from the sensitive circuit to alternative current paths. A large part of effective ESD design is the construction of these switches or trigger elements.

2.5 Decoupling of Current Paths

An additional design method is the decoupling of elements in the ESD current path. Circuit elements can be introduced which lead to the avoidance of current flow to those physical elements. The addition of ''ESD decoupling switches'' can be used to decouple sensitive circuits as well to avoid the current flow to these networks or sections of a semiconductor chip. ESD decoupling elements can be used to allow elements to undergo open or floating states during ESD events. This can be achieved within the ESD network, or within the architecture of a semiconductor chip.

Decoupling of sensitive elements or decoupling of current loops can be initiated by the addition of elements that allow the current loop to ''open'' during ESD events. During ESD testing, power rails and ground rails are set as references. The decoupling of nodes, elements, or current loops relative to the grounded reference prevents over-voltage states in devices, and eliminates current paths. These decoupling elements can avoid ''pinning'' of electrical nodes. Hence, integration of devices, circuits elements, or circuit function that introduce decoupling electrical connections to ground references and power supplies references, is a key unique ESD design practice.

2.6 Decoupling of Feedback Loops

Feedback loops can lead to unique ESD failures and lower ESD results significantly. The decoupling of nodes, elements, or current loops relative to the grounded reference prevents over-voltage states in devices, and eliminates current paths initiated by the feedback elements. These decoupling elements can avoid ''pinning'' of electrical nodes. Hence, integration of devices, circuits elements, or circuit function that introduce decoupling electrical connections to ground references, and power supplies references of the feedback elements during ESD testing is also a key unique ESD design practice.

2.7 Decoupling of Power Rails

Electrical coupling of sensitive nodes to the power supply rails can lead to ESD failure. The electrical coupling of nodes to the power supply rails, ground rails or chip substrate can lead to ESD failure. Semiconductor elements whose nodes are connected to the power supply can establish current paths, constrain electrical potential, establish ''pinning'' of nodes and circuits, or undergo electrical overstress. A key ESD design practice is establishing methods to electrically decouple from power rails to avoid electrical overstress of electrical nodes and components, as well as eliminate undesirable current paths.

2.8 Local and Global Distribution

To provide an effective ESD design strategy, the ESD design practices must focus on the local and global distribution of electrical and thermal phenomena in devices, circuits, and systems. Locally, good current distribution lowers the current density in physical elements.

As the current distribution improves, the local self-heating can be reduced; this increases the margin to thermal breakdown. As the current distributes, the effectiveness of the device helps improving the utilization of the total area of the ESD network or circuit element. On a circuit and system level, the distribution of the ESD current within the network or system, lowers the effective impedance, and lowers the voltage condition within the ESD current loop. The ESD events are transient events; the physical time constants of the devices, circuits, and system are critical in the understanding, modeling, and simulation of the effectiveness of the elements in the system. A key design practice of ESD devices and circuits is the desire to distribute the current to provide improved design utilization to achieve higher ESD robustness.

2.9 Usage of Parasitic Elements

ESD networks are concerned with parasitic devices inherent in the standard devices, or exist between adjacent structures or devices. ESD design either utilizes or avoids activation of these parasitic elements in the ESD implementations. Utilization of parasitic elements is a common ESD design practice for ESD operation. For example, MOSFET structures in wells form parasitic lateral or vertical bipolar transistors with their corresponding wells or substrate regions. Diodes in the substrate can also form lateral bipolar devices with adjacent well regions or devices. Diodes within isolation regions, such as a well, dual-well, or triple-well isolation, can utilize the parasitic elements for the ESD protection scheme. These can include both vertical and lateral parasitic elements inherently within the standard devices and within the technology. It is not common to use these parasitic elements in standard circuit design, whereas for ESD design it is very prevalent to utilize the parasitic devices and is part of the ESD design practice and art.

2.10 Buffering

In ESD design, it is also a common practice to establish current and voltage buffering of sensitive devices, circuits, sub-circuits, chip level core regions, or voltage islands. This can also be done to provide isolation between radio frequency (RF), analog, and digital segments of a semiconductor chip. A design practice is to increase the impedance in the path of the sensitive circuit either by placement of high-impedance elements, establishing ''off'' states of elements, voltage and current dividing networks, resistor ballasting, or initiating elements in high-impedance states.

2.11 Ballasting

Resistive, capacitive, or inductive ballasting can be introduced to redistribute current or voltage within a single element or a plurality of elements, circuit, or chip segment. The usage within a semiconductor device element allows for redistribution within a device to avoid electro-thermal current constriction, and poor area utilization of a protection network or circuit element. The usage of ballasting allows to redistribute the source current from the ESD event to avoid thermal heating or electrical overstress within the semiconductor network or chip. Ballasting can be introduced into semiconductor device structures using the following ESD design methods:

_ Semiconductor process implant design choices (e.g., sheet resistance, profile, dose, and energy).

_ Semiconductor material choice (e.g., titanium vs. cobalt).

_ Use of multiple material phase states (e.g., C49 and C54 titanium phase states).

_ Silicide removal in the direction of current flow.

_ Silicide removal lateral to the direction of current flow.

_ Introduction of resistor elements (e.g., n-diffusion, p-diffusion, n-well, polysilicon film, tungsten local interconnect, and wire resistors).

_ Introduction of elements with positive or negative temperature coefficient of resistance (TCR).

_ Segmentation by introduction of isolation regions.

_ Segmentation by introduction of lateral high-resistance regions in the semiconductor device.

_ Segmentation by introduction of high-resistance regions in the well or substrate regions.

2.12 Unused Sections of a Semiconductor Device, Circuit, or Chip Function

In ESD design, it is common to utilize ''unused'' segments of a semiconductor device for ESD protection, which was not utilized for functional applications. For example, in a ''gate array'' design practice, elements are not connected for functional usage. An ESD design practice is to use them for ESD protection purposes.

2.13 Impedance Matching Between Floating and Non-Floating Networks

In ESD design, it is common to utilize the ''unused'' segments of a semiconductor device for ESD protection and impedance match the network segments for ESD operation; this matching of conditions during ESD testing allows for current sharing during matching between networks and common triggering voltage conditions.

2.14 Unconnected Structures

In semiconductor chips, there are many structures which are electrically not connected to other circuitry or power grids which are vulnerable to ESD damage. In functional designs, these are not a concern. But in ESD design practice, these unconnected structures are locations of potential charging and dielectric breakdown. Hence in ESD design, unique solutions are required.

2.15 Utilization of Dummy Structures and Dummy Circuits

In the ESD design practice it is not uncommon to utilize dummy structures or dummy circuits which serve the purpose to provide better current uniformity or distribution effects; this concepts span from usage of dummy MOSFET polysilicon gate fingers to dummy inverter circuits.

2.16 Non-Scalable Source Events

Another key issue is that the ESD event is a non-scalable event. Each generation, the size of devices are scaled to smaller dimensions. The ESD design practice must address the constant source input current and the physical scaling of the structures. A unique ESD scaling theory and strategy must be initiated to address this issue.

2.17 Area Efficiency

As in power electronic applications, the area of efficiency of a device, or network for redistribution of the ESD current is a key ESD design metric. Area efficiency of a device, network, or chip is important issue in ESD design.

3. TIME CONSTANTS

Time is an important variable in the understanding of ESD phenomena and ESD design.

Time influences the physical phenomenon that is involved, the response of the material, and the response of the semiconductor device, circuit, or chip to the time-dependent ESD phenomena. Time affects the range of the distribution and propagation of the signal, and its distribution through the physical system. Given a physical system, a characteristic length and a characteristic time can be established to explain a physical system. Hence, it is important to understand the time scales, and time constants to comprehend the interaction. As a result, a time constant approach is chosen as a way to introduce the subject of ESD phenomena.

3.1 Characteristic Times

3.2 Electrostatic and Magnetostatic Time Constants

Given a physical system, a characteristic length and a characteristic time can be established to explain a physical system. Let us define a scale of characteristic length l and characteristic dynamical time _. Electrical phenomenon involves both electrical and magnetic fields. The electric and magnetic fields are coupled through Maxwell's equations. Three important time constants allow us to understand the validity of the electrical phenomenon. The three physical time constants of interest are the charge relaxation time, _e, the magnetic diffusion time, _m, and the electromagnetic wave transit time, _em.

3.2.1 Charge relaxation time

Let us define the charge relaxation time, _e

The charge relaxation time is the physical RC time of the medium. It determines how fast a medium responds to an electrical transient state. For example, it determines how well a material screens an electric field from within a medium. This is more apparent when the physical dimensions are added to the time constant.

3.2.2 Magnetic diffusion time

The magnetic diffusion time, _m, is ...

The magnetic diffusion time is the L/R time of the medium. This is a time constant associated with how a medium responds to a magnetic transient state. This is more apparent when put in the following form,

Electromagnetic wave transit time The electromagnetic wave transit time, _em, is the time it takes for an electromagnetic plane wave to propagate a distance l

_em = l c where c is the speed of light in a medium. The speed of light in a medium can be expressed as c = 1

_" p From this we can express the electromagnetic transit time as

__ r The electromagnetic transit time, _em , can then be expressed as,

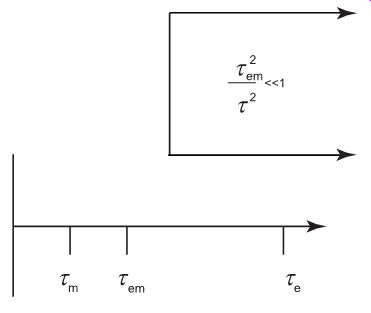

FIG. 1 Electro-quasistatic time constant hierarchy

In this form, the electromagnetic transit time is the arithmetic mean of the magnetic diffusion time and the charge relaxation time. Note that putting in the macroscopic dimensions, we can express this as

In this form, the electromagnetic wave transit time is the square root of the inductance and the capacitance.

Let us define an additional parameter _

_ where the parameter is the ratio of the electromagnetic transit time to the characteristic time. For Maxwell's equations to reduce to the electro-quasistatic (EQS) assumption, the magnetic diffusion time must be less than the charge relaxation time and the characteristic time _ must be much greater than the electromagnetic transit time. FIG. 1 shows the electro-quasistatic time constant hierarchy.

In the majority of ESD concerns which is of interest in the scope of the text, electrostatics and electro-quasistatics are valid. The characteristic time scale of an ESD pulse will be of the order of a nanosecond to tens of nanoseconds, which is significantly longer than the electromagnetic transit time of a semiconductor device, circuit, or chip. For semiconductor, the substrate materials are such that the charge relaxation time is longer than the magnetic diffusion time as a result of the magnetic permittivity values and electrical permittivity. As the analysis addresses electrical interconnects, packaging, and transmission line pulse systems, the characteristic time approaches the electromagnetic transit time. In the analysis of ESD events involving the arc discharge, both current phenomena and electromagnetic emissions are present of a TE, TM, and TEM form.

For Maxwell's equations to reduce to the magneto-quasistatic (MQS) assumption, the charge relaxation time must be less than the magnetic diffusion time and the characteristic time _ must be much greater than the electromagnetic transit time. In most ESD problems, the analysis does not involve the MQS analysis. But, there are some cases, such as magnetic recording media, magnetic memory, and MRAMs, where the MQS assumption is valid.

3.3 Thermal Time Constants

ESD phenomena is both electrical and thermal in nature. The time regimes of thermal analysis is divided into three regimes, based on the thermal diffusion time. These regimes are known as the adiabatic time regime, the thermal diffusion time regime, and the steady-state regime. These regimes directly follow from the assumption of the relative time scales compared to the thermal diffusion; this directly follows from the solution of the partial differential equation known as the thermal diffusion equation.

3.3.1 Heat capacity

Heat capacity of a medium is the ability of a medium to store energy. The heat capacity of the system is expressed as the product of the mass density, _, the specific heat, cp, and temperature

3.3.2 Thermal diffusion

Thermal transport occurs as a result of a gradient in the temperature field. Thermal conduction occurs as a result of thermal diffusion.

3.3.3 Heat transport equation

ESD phenomena involves both electrical and thermal phenomena. The temperature field in a medium can be determined from the differential equation of heat conduction. The temperature at any point in the medium can be quantified by understanding the energy balance in a given region. The energy-balance equation for an infinitesimal volume is determined by the sum of the net rate of heat entering the volume, and the rate of energy generation in the volume, which is equal to the rate of increase of the internal energy in the volume. The net rate of heat entering the infinitesimal volume is equal to the heat flowing into the volume and the heat flowing out of the volume. The sum of the differential heat flow in all directions determines the net rate of heating in the volume. This term is the divergence of the heat flux. The rate of energy generation in the volume is associated with the generation sources in the infinitesimal. The rate of increase in the internal energy is associated with the increase in the heat capacity of the system. The energy balance equation in this form is also known as the heat equation, or the partial differential equation of heat conduction,

In the case that the thermal conductivity, k, is position and temperature independent, the thermal conductivity variable can be separated from the heat flux term. In this case, the partial differential equation of heat conduction can be normalized. The heat flux term can be simplified as the Laplacian of temperature and expressed as ...

In this form, the thermal diffusivity is defined as ...

This equation in this form is important for quantifying the ESD event in the location where the heat generation is occurring. This is typically in the region of electrical current fluence or electrical current generation. For example, heat is generated in the source, drain, and channel of a MOSFET as a result of Joule heating.

Given that there is no internal generation of heat sources inside the medium, the partial differential equation of heat conduction can be simplified to the Fourier equation, also known as the diffusion equation.

The Fourier equation is also known as the parabolic equation since it is a differential equation which is first order in time and second order in space. For ESD analysis, this equation is applied in regions where there are no sources of thermal generation, yet whose temperature field is being influenced by heat flux or temperature gradients inside the regions or on its boundaries.

For steady-state processes, the partial differential equation of heat conduction simplifies to...

For the case of a uniform thermal conductivity (space and time), the partial differential equation of heat conduction reduces to the Poisson equation with temperature as the field variable. The Poisson equation is valuable for analysis of self-heating processes which are steady state. In the case that there is no internal generation, uniform thermal conductivity, and no heat generation, the Poisson equation simplifies to the Laplace equation r2 T = 0 1.3.4 Thermal Physics Time Constants From the partial differential equation of heat conduction, a characteristic time associated with thermal diffusion is the thermal diffusion time, _T,

...where...

...is the thermal diffusivity,

= k=_cp and l is the characteristic length. Given an oscillatory steady-state thermal excitation which has an angular frequency, omega , where the spatial wavelength is much shorter than other physical characteristic lengths, a thermal skin depth can be defined as ...

3.4.1 Adiabatic, thermal diffusion time scale and steady state

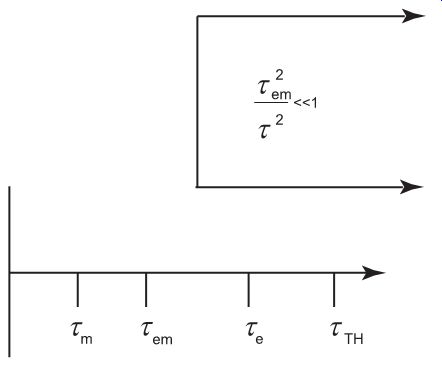

FIG. 2 Electro-quasistatic and thermal time constant hierarchy

ESD phenomenon in semiconductors concerns itself with events where the time scale of the applied pulse and response of the medium, circuit, and systems are of primary interest.

The hierarchy of characteristic times must be established to understand the physical phenomenon and the relationship of the ESD event characteristic times. The characteristic time of the ESD event relative to the electromagnetic wave transit time, the charge relaxation time, the magnetic diffusion time, and the thermal diffusion time are important to understand the physical response.

In semiconductors such as silicon, the hierarchy of characteristic times follow the EQS assumption. FIG. 2 shows the electro-quasistatic and thermal time constant hierarchy.

For an EQS assumption, the magnetic diffusion time is shorter than the electromagnetic transit time. The ordering of characteristic times are the magnetic diffusion time, the electromagnetic transit time, and then the charge relaxation time. Additionally, the time region of interest is such that the electromagnetic transit time is significantly smaller than the characteristic time of the pulse (e.g., 1). The ordering of these characteristic times must be true to insure validity of the EQS assumption. To address the issue of thermal transport, there are three regions of interest within this hierarchy of characteristic times. When the characteristic pulse time, _, is much shorter than the thermal diffusion time, the thermal transport due to conduction is negligent. This is the ''adiabatic assumption.'' As the characteristic pulse time, _, is of the same order of magnitude as the thermal diffusion time, the hierarchy of the time scales is such that _ ~ O. This will be referred to as the

''thermal diffusion regime assumption.'' As the characteristic pulse time is significantly longer than the thermal diffusion time, the solution approaches a steady-state response known as the ''steady-state assumption.''

3.5 Semiconductor Device Time Constants

3.5.1 Depletion region transit time

For the diode depletion region transit time, the time it takes to traverse the depletion width is a width of the depletion region divided by the drift velocity of the carrier,

_t = Wd vd

where the depletion width can be expressed as a function of the doping concentration on both sides of the metallurgical junction,

1 2 and the drift velocity can be expressed as the product of the mobility times the peak electric ...

field, vd = _jEj

The peak electric field in the junction can be expressed as a function of the voltage across the depletion region, and the doping concentrations, Epeak

This time constant is important in that it is a key time constant when a diode element is used as an ESD element, or a switching element. This is of greater concern in addressing high-speed ESD phenomena such as the charged device model (CDM) events.

3.5.2 Silicon diode storage delay time

In the switching of a silicon diode, stored charge in the base region can limit the diode speed.

The diode storage delay time can be expressed as, ...

which is the product of the recombination time of a p+n diode, and the inverse error function of the ratio of the forward and reverse currents. Note that this time constant is a function of the current in a semiconductor device, and can be limiting during fast ESD events.

3.5.3 Bipolar base transit time

The bipolar base transit time is the time for a carrier to diffuse across the base region. This is equal to the base width divided by the diffusion velocity; this can be expressed as a function of the base width and the diffusion coefficient,

...where WB is the base width, and D is the diffusion coefficient. This time constant is important for the understanding of the time response of a bipolar transistor.

3.5.4 Bipolar turn-on transient time

For the turn-on transient of a bipolar transistor, the time constant is a function of the recombination time, the base current, and collector current ...

3.5.5 Bipolar turn-off transient time

For the turn-off transient time of a bipolar transistor, the time constant is a function of the recombination time, the base current, and collector current.

3.5.6 Bipolar emitter transition capacitance charging time

In a bipolar transistor, there is a finite ''RC'' time for the response of the emitter. The response of the emitter is a function of the emitter resistance, rE, and the associated emitter capacitance at zero bias voltage …with emitter resistance equal to the thermal voltage divided by the emitter current

rE = kT qIE

...and the capacitance is the dielectric constant divided by the depletion width (at zero volts) CTE

3.5.7 Bipolar collector capacitance charging time

The bipolar collector capacitance charging time is analogously similar to the emitter capacitance charging time. The bipolar collector charging time is associated with the collector resistance (e.g., sub-collector resistance) and the collector capacitance. This can be expressed as ...

3.5.8 Silicon controlled rectifier (SCR) time response

Silicon controlled rectifiers (SCR) are used as ESD protection circuits on input nodes and power supplies. The time response of the SCR circuit is the sum of the base transit times across the pnp and npn bipolar transistor elements ...

__ 2Dn and for the npn bipolar device, the base transit time is ...

3.5.9 MOSFET transit time

The MOSFET device has characteristic time constants associated with the transport of the carriers from the MOSFET drain to the source. The MOSFET channel transit time is equal to the MOSFET effective channel length, Leff, divided by the carrier drift velocity, vd, in the channel

_t = Leff vd

The carrier drift velocity is equal to the product of the electron mobility and saturation electric field.

vd = _Esat where the saturation electric field, Esat, is equal to the MOSFET source-to-drain voltage divided by the MOSFET effective channel length, Leff. The MOSFET source-to-drain transit time can be expressed as the ...

MOSFET drain charging time

The MOSFET drain charging time is the time it takes to charge up the drain node of a MOSFET. This is important in ESD networks in that for the MOSFET snapback voltage, there is a finite time for the MOSFET drain to rise. The MOSFET drain rise time is equal to the MOSFET drain resistance and the MOSFET drain capacitance. The drain resistance is a function of the MOSFET drain sheet resistance, the MOSFET width, and the number of MOSFET fingers. The MOSFET drain capacitance is a function of the MOSFET channel width, the number of MOSFET fingers, and the MOSFET drain junction capacitance per unit area.

This time constant is important in understanding the drain response during ESD events when a MOSFET structure is used as an ESD element, or in ESD MOSFET drain-coupling networks.

3.5.11 MOSFET gate charging time

The MOSFET gate charging time is the time it takes to charge the MOSFET gate electrode.

This will be a function of the MOSFET gate resistance and the MOSFET gate-to-channel capacitance. The gate resistance is a function of the polysilicon MOSFET gate sheet resistance, the MOSFET channel length, the MOSFET width, and the number of MOSFET fingers.

The MOSFET gate capacitance is a function of the MOSFET channel length, MOSFET channel width, the number of MOSFET fingers, and the gate capacitance per unit area

3.5.12 MOSFET parasitic bipolar response time

During ESD events, the parasitic bipolar transistor plays a role in the response of a MOSFET transistor. The MOSFET bipolar base transit time is the time for a carrier to diffuse across the MOSFET drain to the MOSFET source, in the channel region. This is equal to the MOSFET channel length divided by the diffusion velocity in the MOSFET channel region;

this can be expressed as a function of the MOSFET channel length, Leff, and the diffusion coefficient, D, in the MOSFET channel region

This time constant is important in the understanding of the response of a MOSFET during fast ESD events.

3.6 Circuit Time Constants

3.6.1 Pad capacitance

In the analysis of the ESD response, the capacitance of the pad acts as a load in the ESD analysis. The pad capacitance influences the RC time of the network Cload = Cpad

3.6.2 Half-pass transmission gates (TG)

The understanding of the time delays of the half-pass transmission gates is key to the response to receiver networks. Additionally, the time delays are also associated with the CMOS inverter propagation delay times.

3.6.3 n-Channel half-pass transistor charging time constant

The time delay in charging a output capacitance load, Cout, with a transmission gate voltage equal to VDD, has a n-channel half-pass transmission gate charging time of ...

...where the output voltage through the half-pass transmission gate can be expressed as ...

3.6.4 Half-pass transistor transmission gate discharge time constant

The half-pass transistor transmission gate discharge time constant to pass a logical ''0'' has a discharge time constant equal to ...

...where the voltage at the output of the half-pass transistor has the form ...

3.6.5 p-Channel half-pass transistor charging time constant

For the case of the p-channel half-pass transistor transmission gate, the charging and discharging time constants are analogous but opposite in form. For transmission of a logical…

…where…

For transmission of a logical ''0,'' the discharge event can be expressed where the output voltage through the half-pass transmission gate can be expressed as …

3.6.6 Inverter propagation delay time constants

The propagation time constants associated with an inverter has the same nature as the time constants associated with the half-pass transmission gates. In an inverter, the charging and discharging of the load occurs through the p-channel MOSFET or the n-channel MOSFET identical to the half-pass transistor.

3.6.7 High-to-low and low-to-high transition time

The high-to-low transition time can be defined as a function of the charging and discharging times of an half-pass transmission gate (V0 is 10% transition point of VDD, or 0.1 VDD)

3.6.8 Inverter propagation delay time

The CMOS inverter propagation delay time can be represented as […]

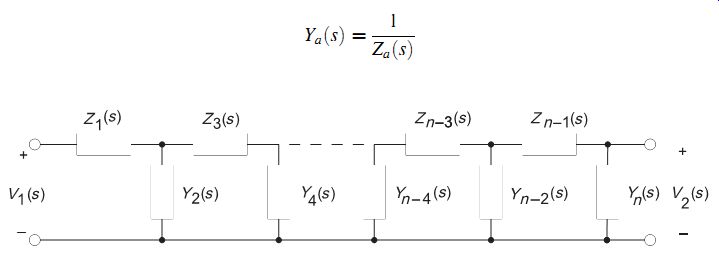

3.6.9 Series n-channel MOSFETs discharge delay time

Given a set of n-channel transistors in a series configuration, the transistors serve as a series of half-pass transistors. The transistors each have a corresponding diffusion capacitance from the MOSFET source and drain diffusion; each MOSFET channel region serves as the series resistance element. To evaluate the delay time constant for a series-connected MOSFETs this can be treated as a lumped RC transmission line or RC ladder network. A simplified solution for N transistors in a series configuration, the delay time can be estimated as the superposition of time constants […]

For each time constant in the expression, the i th element in the RC ladder network is the product of the i th capacitor element and the summation of all the resistances to the i th element, ...

...where for n-channel MOSFET devices

3.6.10 Series p-channel MOSFETs charge delay time

Given a set of p-channel transistors in a series configuration, the transistors serve as a series of half-pass transistors. The transistors each have a corresponding diffusion capacitance from the MOSFET source and drain diffusion; each MOSFET channel region serves as the series resistance element. As in the n-channel case, to evaluate the delay time constant for a series connected MOSFET, this can be treated as a lumped RC transmission line, or RC ladder network. A simplified solution for N transistors in a series configuration, the delay time can be estimated as the superposition of time constants ...

For each time constant in the expression, the ith element in the RC ladder network is the product of the ith capacitor element and the summation of all the resistances to the ith element

3.7 Chip Level Time Constants

On the semiconductor chip level, the critical chip time constants of interest to ESD protection is the global time constants and the package level time constants:

_ Peripheral I/O power bus time constant.

_ Core chip power grid time constant.

_ Substrate time constant.

_ Package level time constants.

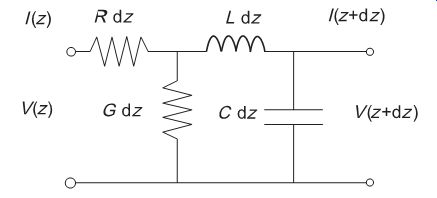

3.7.1 Peripheral I/O power bus time constant

During ESD events, the current flows through the ESD network to the power bus. Along the power bus is a plurality of peripheral circuit books. The peripheral circuits contain pads, ESD networks, and the receiver or transmitter books. The peripheral power bus extends over these circuits in a regular spacing. Hence, we can represent the power bus time constant as a RC ladder network. The incremental resistor element is the bus resistance between adjacent peripheral I/O cells, and the incremental capacitance element is the loading of the individual peripheral circuits books, and the bus capacitance. The incremental bus resistance is ...

where L is the spacing between adjacent I/O cells, Wbus is the bus width. The incremental capacitance is the incremental bus capacitance term and the book capacitance C = Cbus + Cbook and incremental capacitance

Cbus = "eff LWbus d

The number of external pins can be estimated from the number of circuits in the semiconductor chip according to Rent's Rule

Np = KpN g

where Np is the number of external pins, Ng is the number of total gates, and Kp and are proportionality constants. From the knowledge of the chip size and the number of circuits, the number of pins along the bus can be estimated.

3.7.2 Core chip time constant

The response time of the core chip is a function of the total chip capacitance. The chip capacitance is proportional to the number of circuits and the capacitance per internal circuit.

From Rent's Rule, knowing the number of I/O pins, we can estimate the number of internal circuits.

From this expression, knowing a capacitance of a typical inverter circuit, the loading effect on the power grid can be estimated. Assume the loading capacitance of a typical network is Cg , an estimate of the total circuit capacitance loading can be expressed as Cg.

The total chip capacitance can also include the decoupling capacitors that are added to increase the total chip capacitance.

In evaluation of the chip response, the resistance and the capacitance both play a role. The estimate of the resistance is a function of the architecture and chip design methodology. Hence, there is an RC time associated with the chip response.

3.7.3 Substrate time constants

The response of the chip substrate also plays a role in ESD phenomenon. On a global level, the substrate time constant is a function of the substrate resistance and the substrate contact density. From Rent's Rule, we can project the number of substrate contacts in the core of the chip from the knowledge of the internal number of circuits. Knowing the number of internal gates, we can assume that there is a substrate contact for some proportionality constant for every circuit. This is a valid assumption, since for latchup it is required to have a local substrate contact within a given distance from all circuits, assuming some proportionality constant,

Nsx ()Core= Ng

The spacing of the substrate contact relative to the circuit and the size of the average internal circuit will lead to the defining of the proportionality constant. Additionally, for the peripheral circuits, we can assume each I/O circuit has a substrate contact

Nsx ()I=O= KpN g

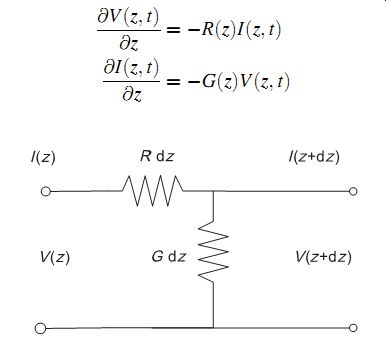

The incremental resistance between substrate contacts will be a function of the chip area, the contact-to-contact spacings, and the substrate resistance. This network will form a two dimensional resistance grid. Hence the substrate network will primarily be a time constant associated with a resistance network. The resistance distribution will respond as a resistance-conductance (RG) transmission line. For the substrate, the capacitance formed between the substrate and the package has a role in the capacitance coupling during a charged device model (CDM).

3.7.4 Package time constants

In ESD events, packages have an influence on HBM, MM, and CDM events. The package can be modeled as a capacitor-inductor lumped parameter. A typical package model will consist of a _-network, consisting of a first shunt capacitor, a series inductor, and a second shunt capacitor element. In some package designs, the lead frames and wire bond also serve as a series inductors elements. At high frequencies or packages with high inductance, the package can influence the ESD event waveform and the circuit response.

3.8 ESD Time Constants

3.8.1 ESD time constants

To understand physical phenomena, and particularly ESD phenomenon, it is necessary to quantify the scale in both space and time. ESD phenomena involves microscopic to macroscopic scales. ESD phenomena involves electrical and thermal transport on the scale of nanometers, circuits and electronics on the scale of micrometers, semiconductor chip designs on the scale of millimeters, and systems on the scale of meters. The time scales of interest range from picoseconds (ps) to microseconds (ms). Electrical currents of interest range from milliamps (mA) to tens of amperes (A). The voltage range of interest varies from volts (V) to kilovolts (kV). Temperatures vary from room temperature to melting temperatures of thousands of degrees Kelvin. It is the vast ranges of time, space, currents, voltages, and temperature as well as its transition from the microscopic to the macroscopic which makes ESD phenomenon difficult to model, simulate, and quantify.

To comprehend ESD phenomenon and establish validity of analytical developments, it is important to be able to understand what phenomenon is important. By analyzing the physical equations from a time constant approach, equations and understanding can be made both rigorous as well as improve logical clarity.

3.8.2 ESD events

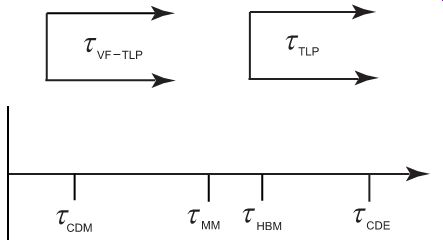

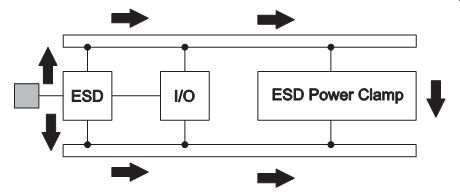

To understand the role of ESD events and the physical environments, it is important to quantify the characteristic times of an ESD event. ESD events are represented as circuit equivalent models. FIG. 3 contains the ESD time constant hierarchy.

3.8.3 Human body model characteristic time

A fundamental model used in the ESD industry is known as the HBM pulse. The model was intended to represent the interaction of the electrical discharge from a human being, who is charged, with a component or object. The model assumes that the human being is the initial condition. The charged source then touches a component or object using a finger. The physical contact between the charged human being and the component or object allows for current transfer between the human being and the object. A characteristic time of the HBM is associated with the electrical components used to emulate the human being. In the HBM standard, the circuit component to simulate the charged human being is a 100 pF capacitor in series with a 1500 ohm resistor. This network has a characteristic rise time and decay time. The characteristic decay time is associated with the time of the network

_HBM = RHBMCHBM

where RHBM is the series resistor and CHBM is the charged capacitor. This is a characteristic time of the charged source. A more accurate understanding of the waveform and time constant is needed to evaluate the circuit response. The RC time constant only addresses the decay time of the waveform, and does not quantify the rise time. A more accurate representation of the HBM event addresses the series inductance. Roozendaal treated the HBM waveform as a lumped RLC network consisting of the source capacitor, a series inductor, and series resistor. The current as a function of time from the HBM event can be expressed as a double exponential waveform

The addition of the inductor introduces an L/R time constant into the HBM waveform expression. This can also be expressed in as a hyperbolic form as the solution of the RLC network

FIG. 3 Electrostatic discharge (ESD) time constant hierarchy

...where the resonant frequency is …

For the HBM pulse waveform, the R/2L time constant is greater than the LC resonant time constant. The rise time is dominated by this time constant, where…

The inductance in the HBM simulators are in the range of 5-10 mH, leading to rise times of the order of 17-22 ns.

3.8.4 Machine model characteristic time

Another fundamental model used in the ESD industry is known as the machine model (MM) pulse. The model was intended to represent the interaction of the electrical discharge from a conductive source, which is charged, with a component or object. The model assumes that the ''machine'' is charged as the initial condition. The charged source then touches a component or object. In this model, an arc discharge is assumed to occur between the source and the component or object allowing for current transfer between the charged object and the component or object. A characteristic time of the machine model is associated with the electrical components used to emulate the discharge process. In the MM standard, the circuit component is a 200 pF capacitor with no resistive component. An arc discharge fundamentally has a resistance on the order of 10-25 ohm. The characteristic decay time is associated with the time of the network

…where R is the arc discharge resistor and C is the charged capacitor. This is a characteristic time of the charged source.

The simplified expression does not address the waveform observed from test simulators.

The MM waveform contains both oscillation and an exponential decay. The current waveform as a function of time for the simulated MM pulse is ...

In this form, it is apparent that the waveform peak is a function of the initial voltage on the source capacitor. The oscillatory nature of the MM waveform is a function of the LC time constant. The damping factor is a function of the R/L time constant; as the R/L time constant increases, the current waveform decays at a faster rate.

3.8.5 Charged device model characteristic time

The CDM represents an ESD interaction between a chip and a discharging means where the chip is pre-charged. The charging process can be initiated by direct charging or field-induced charging. The discharge process is initiated as contact is initiated between the charged device and the discharging means.

3.8.6 Charged cable model characteristic time

Another fundamental model used in the ESD industry is known as the charged cable model or cable model pulse. The model was intended to represent the interaction, the electrical discharge of a charged cable, discharging to a chip, card or system. To initiate the charging process, a transmission line or cable is dragged on a floor leading to tribo-electric charging.

The model assumes that the cable is charged as the initial condition. The charged cable source then touches a component or object. A characteristic time of the cable model is associated with the electrical components used to emulate the discharge process. In the charged cable model, the cable acts as a capacitor element. The characteristic decay time is associated with the time of the network

...where R is the discharge resistor and C is the charged cable. The capacitance used for this model is 1000 pF. In early development times, this model was treated as an RC response model, where a very large capacitor represented the cable.

3.8.7 Cable discharge event (CDE) model

In recent years, this model has evolved into the cable discharge event (CDE) model.

In early development, this was a concern for large system cables. System level engineers are required to improve system-level performance while maintaining the quality and reliability.

ESD and electromagnetic emissions (EMI) are a concern in systems. System level standards and system engineers have long known that charged cables can also introduce system-level concerns. Charge accumulation on unterminated twisted pair (UTP+ cables occur through both tribo-electric charging and induction charging. In the case of tribo-electrification, in a UTP cable can be dragged along a floor. A positive charge is established on the outside surface of the insulating film. The positive charge on the outside of the cable attracts negative charge in the twisted pair leads across the dielectric region. When the negative charge is induced near the outside positive charge, positive charge is induced in the electrical conductor at the ends of the cable. As the cable is plugged into a connector, electrical arcing will occur leading to a charging of the unterminated twisted pair (note: the twisted pair was neutral to this point). If a cable is introduced into a strong electric field, induction charging will occur. When the electric field is removed the cable remains charged until a discharge event from grounding occurs. With the integration of wide area networks (WAN), and local area network (LAN), the Ethernet is playing a larger role. When a charged twisted pair cable connects to an Ethernet port with a lower electrical potential, cable discharge events can occur in LAN systems. In the past, standards (e.g., IEEE 802.3 Section 14.7.2) have noted the potential for CDE processes in LAN cables. Additionally, the introduction of Category 5 and Category 6 cables have significantly low leakage across the dielectric. As a result, when a tribo-electric charge is established, the conductance of the insulator is so low that the induced charge can maintain for long time scales (e.g., 24-h period). The CDE produces a rectangular pulse whose pulse width is a function of the length of the cable, L.

The pulse width can be expressed as follows:

3.8.8 Charged cassette model characteristic time

The charged cassette model (CCM) is a recent model associated with consumer electronics.

In consumer electronics there are many applications where a human plugs a small cartridge or cassette into a electronic socket. These are evident in popular electronic games. In today's electronic world, there are many palm-size electronic components which must be inserted into a system for non-wireless applications. To verify the electronic safety of such equipment, the cassette itself is assumed as a charged source. The ''cassette model'' assumes a small capacitance and negligible resistance. This model is equivalent to a machine model type current source with a much lower capacitor component. The model assumes the resistance of an arc discharge and a capacitance of 10 pF.

3.8.9 Transmission line pulse (TLP) model characteristic time

Transmission line pulse (TLP) testing has seen considerable growth in the ESD discipline. In this form of ESD testing, a transmission line cable is charged using a voltage source. The TLP system discharges the pulse into the device under test (DUT). The characteristic time of the pulse is associated with the length of the cable.