By Forest Belt

Whether in a factory maintenance shop or at a consumer electronics bench, you must under stand these basic characteristics of digital signals before you can troubleshoot effectively.

Not everyone knows that some digital signals are simple dc voltages. The following explanations should be helpful as a review, or they could improve your expertise by bringing complete understanding of scoping digital signals.

Signals for TTL and CMOS devices are made up of only two digital states. They go by various terms. Sometimes they're called high and low, on and off, or up and down. In books, magazine articles and truth tables, you find the shorthand symbols: 1 and 0.

The terms logic-high and logic-low appear often. Digital circuitry follows the principles of binary logic set forth by George Boole. His two-number math system (called Boolean algebra) belongs mainly to the theoretical or design side of digital electronics. You can service digital equipment expertly without mastering binary arithmetic, so don't let the mathematics turn you off.

TTL and CMOS

By way of background, you should know that most digital electronics use two different kinds of devices. One category involves silicon diodes, bipolar transistors and regular resistors. These are in a family labeled TTL, for transistor-transistor-logic.

The other group incorporates metal-oxide semiconductor (MOS) materials. These are often placed in a complementary configuration, giving the term CMOS for this family of digital-electronic devices.

Signals handled by the two families of logic devices are similar, but their logic levels or voltages differ considerably. For TTL logic, a high condition exists when signal voltage exceeds 3V or so, with 4V considered optimum for dependable operation of TTL gates and latches.

CMOS logic devices need 13V or so for a distinct high condition. Logic-low in both families is below IV.

Between the low and high logic levels is a limbo area producing indeterminate operation. A gate cannot be depended on to function predictably when voltages do not rise to the full level for logic highs or drop close to zero for logic lows.

In practical circuitry, logic-high levels may vary as much as a volt or two from the 4V and 13V amplitudes.

Steady-state digital signals

Some technicians find it vaguely difficult to think of steady dc voltages as signals. Yet in digital usage, dc frequently constitutes a signal.

This phenomenon has several viewpoints. On the one hand, you might think of a logic-circuit device as being signaled to turn on or off by input of a particular logic level-either high or low.

Consider just one example.

Switching logic often uses an OR gate. A logic-high dc voltage applied to either input turns on an OR gate, forcing its output logic-high. The dc input voltage acts as a signal. It signals the gate to turn on, and to place logic-high at its output terminal.

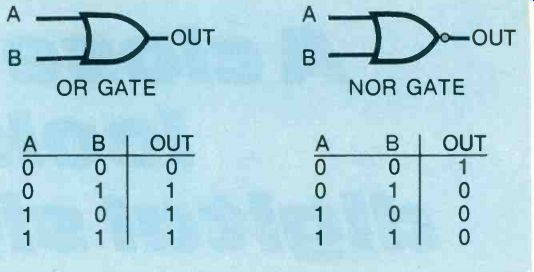

Truth tables, such as those in Figure 1, tabulate the output responses of digital-logic devices to various steady-state dc input signals. The first table shows OR-gate functions. Either or both inputs with logic-high states will signal the OR gate to output a logic-high.

Two logic-lows call for a logic-low output.

A NOR gate acts as an OR gate that has its output inverted. A logic-high at either or both inputs turns an a NOR gate. However, an operating NOR gate has a logic-low output because of inversion. (Only a logic-low at both inputs gives a logic-high output). A low output is equivalent to a ground signal for any stage or device that is connected to it.

Perhaps you are familiar already with the actions and truth tables of all digital-logic gates. The vital point is that the steady dc states described here are actually digital signals. With some practice, you should find it easy to think this way about steady-state dc input and output voltages: they are real signals. Although a certain reorientation of thinking is required, it is crucial to understanding the next step.

Effects of timing

One element has been omitted from the foregoing discussion. Voltage and amplitude (logic level) are mentioned, but not the element of time. And time is a vital factor that must be considered in connection with any signal. As it turns out, timing is actually more important to digital-electronic signals than is voltage amplitude.

A steady-state signal almost seems to have no time element. By its very name, this kind of dc signal either appears to be there or not. A given circuit point or terminal is either on (logic-high) or it is off (logic-low). The circuit either has voltage present, or it is grounded.

But remember that the point or terminal has to be forced to one signal condition or the other. And, since there are only two conditions, the circuit always goes from logic-low to logic-high or from logic-high to logic-low.

The matter of timing enters the picture when you become concerned with how long a circuit point or terminal remains in one logic condition or the other.

What has been described as steady-state logic levels are really digital signals with long time durations. Suppose the OR gate in Figure 1 were to have a logic-high applied to input A. Output immediately goes logic-high, and stays there until the input high is removed. This could be anytime from a fraction of a second later, to an hour or years.

Now consider the effects of input timing. Suppose the high at input A lasts for 10 minutes. Output will stay logic-high at least that long.

Nine minutes after input A goes high, imagine that input B also receives a logic-high signal. Nothing changes right then, since the gate output already is logic-high.

But what happens if the B-input signal has a duration of six minutes? The OR-gate output stays high for a total of 15 minutes.

That's nine minutes from A input alone, one minute while both inputs are high, and another five minutes until input B goes back to logic-low.

Figure 1---Truth tables show, in tabular form, the functions of logic

symbols and devices, and are clues to what you can expect from digital

signals of the steady-state variety.

When digital signals are applied to actual logic devices, their effects (even those from steady-state signals of long durations) might overlap.

Indeed, they are intended to overlap. Timing is vitally important in digital electronics.

Steady-state signals are dc voltages (or grounds) applied for certain purposes. Then, when different conditions are desired, the steady-state signals are altered to arrange the new circuit conditions.

The signals may be shifted manually by some operator, other circuits or timing devices. But the combinations and timing of dc logic signals often are crucial to operation of any number of stages, circuits, and sections in an electronic system, whether simple or complex.

Cycles and timing

To display digital signals properly on a triggered scope, a technician needs a genuine understanding of signal timing. Again, this discussion may seem basic. But continue with the review, anyway. It will help orient thinking for the best analysis of waveforms in digital-electronic circuits. In fact, you'll gain a lot of familiarity if you duplicate these displays and exercises on your own scope.

Start with a signal that is not digital, but is very common: a sine wave. It can come from any audio generator.

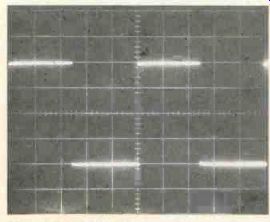

Figure 2A shows how the sine wave should appear on your scope.

The signal voltage rises gradually and steadily from zero (at the centerline) to a positive peak, whatever that value may be. Then the voltage trace rolls over the peak and falls smoothly back to zero.

Continuing on, the sine-wave voltage builds to a peak in the negative direction, and then rises just as smoothly again to zero. This constitutes one cycle.

But that's only part of the description. A time element is involved too. To view the sine-wave signal on a scope, a certain time base must be selected. Suppose the sine-wave frequency is the common 60Hz. Set a time base of 2ms/div on the scope, and measure time along the X-axis of the scope graticule.

The rise of voltage from zero to a positive peak occupies a bit more than two X-axis divisions, or 4ms.

The gradual fall from peak back to zero voltage takes another 4ms. The negative peak is reached more than 4 ms later, and the cycle ends at zero some 16-plus milliseconds after it started. Actual measurable duration of one entire sine-wave cycle is 16.667ms.

Another example brings you closer to the principle of digital-electronic signals. Feed a 1000Hz square-wave signal into a triggered scope. Set the scope sweep for a time base of 0.2 ms/div. To make analysis easy, make trigger polarity or slope positive (4-) and set trigger level anywhere on the first upslope of the signal waveform. The display should resemble Figure 2B.

Here's how to approach analysis of this waveform. First, ascertain its amplitude. What setting has been used for the scope's input attenuator? (Be sure the input variable knob is at the calibrated end of its rotation.) Count the vertical (Y-axis) divisions occupied by the signal. In Figure 2B, the waveform is roughly five divisions high, and the input knob was set at 0.1 volt/div Multiply five divisions by 0.1V for each one, and you get 0.5V peak-to-peak amplitude. As it happens, a 10:1 probe was in use. So the actual amplitude of signal at the probe tip is 5V peak-to-peak.

Next, measure signal timing. One cycle of this square wave begins as the trace is swept upward from zero-base at the graticule centerline.

The trace rises 2 1/2 divisions, re mains there for 2 1/2 horizontal (X-axis) divisions, falls back to zero-center, and then continues another 2 1/2 vertical (Y-axis) divisions to its negative-direction maximum. There the trace amplitude holds while the sweep covers an other 2 1/2 divisions along the time base. Then, rising back to zero-center, the trace ends one cycle.

Considered in this fashion, one cycle of this 1000Hz square wave appears to take up five divisions along the X-axis of the graticule.

With each division representing a time base of 0.2ms, this means each whole cycle takes 1 ms to occur.

Digital signal timing

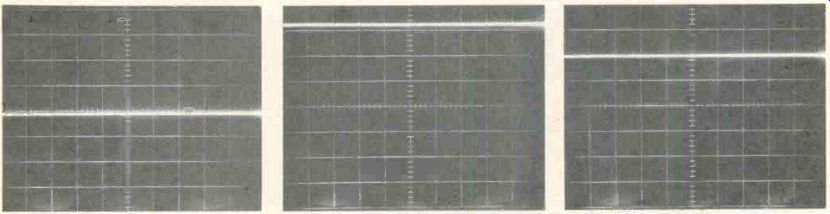

Actually, the description just given is an outmoded way of "seeing" signals of this kind. They are more easily understood in digital terms. Take a look at the waveform in Figure 3. It appears very similar to the square wave of Figure 2B.

In one sense, they are much the same. Amplitude is close, and in timing they look exactly alike. But the signal in Figure 3 does not come from an audio or square-wave generator. It is created by a pulse generator. It is, in reality, a digital signal. It should be analyzed in a digital way.

Figure 2---Sine and square waves are the more ordinary signals most technicians

have studied on their scopes. Principles of timing and cycle duration

have some bearing on digital signals, too, but must be considered in

a different manner.

Digital signals, remember, have only two states: on or high, and off or low. In Figure 3, those are the only two conditions visible. Zero, instead of being at the graticule centerline, is based two divisions lower. That's where the trace rests when no digital voltage deflects it upward, when the digital signal from the generator is off or at logic-low.

When the digital-pulse signal turns on, the scope beam moves suddenly upward. As the generator holds the signal high for a certain period, the scope sweep moves the trace sideways. After a finite period of time, the generator turns off.

The sweep beam moves almost instantly back downward to the zero base line, two divisions below center. With those mechanics in mind, you can analyze the digital waveform in Figure 3.

First, amplitude. The scope's input attenuator still is at 0.2volt/div. The signal covers two divisions on the Y-axis. With the 10:1 probe in place, therefore, signal amplitude is 4V.

Notice the term peak-to-peak was omitted this time. That's because digital signals are either off (zero volts) or on (peak voltage). The digital signal displayed in Figure 3 is for TTL or related families of logic circuits. Its logic-low condition is at or near zero volts, which serves as the base line for the scope trace.

The logic-high condition occurs at 4V, the on amplitude. Hence, this digital signal is said to have an amplitude of 4V.

Now analyze the timing of the digital signal in Figure 3. For digital signals, you are interested in two conditions: on and off The signal is on when amplitude is 4V, off when amplitude drops to zero or near zero.

To study a digital signal, you set a time base on the scope that allows a measurement of both on and off times of the signal. In Figure 3, a time base of 20ps/div makes the display seen.

The logic-high time duration, sometimes called pulse width, covers 2 1/2 divisions on the X-axis. At 20ps/div, that figures out to 50 ps of logic-high.

Then the generator turns the signal off, and the trace drops to zero, along the base reference line.

The scope trace keeps moving sideways, swept by the scope time-base generator. So the lower trace represents off or zero-amplitude time. Duration of this logic-low time also covers 21/2 divisions. So off-time, too, is 50us.

So, Figure 4 is a 4V digital signal with on-time of 50ps and off-time of 50 s. The digital signal stays on just half of the time, and is said therefore to have a duty cycle of 0.5 or 50%.

On duty or off? This matter of logic–high-time versus logic-low time in a digital signal proves critical in many electronic systems. It needs deeper examination.

To cause the scope display pictured in Figure 4A, a digital signal has risen to logic-high; keeps the beam deflected at logic-high for the length of time it takes the sweep to cross two graticule divisions; then falls to logic-low; and stays logic-low for a duration of one division.

Then the two-division logic-high pulse recurs, followed by another one-division period of logic-low; and so on. Each complete cycle or logic-high/logic-low covers three graticule divisions. This pulse series is considered repetitive, as it keeps repeating its pattern.

Figure 3 Looks like a square wave, but it's not. This signal is digital,

with a duty cycle that leaves it on half the time and off the other half.

Figure 4---Examples of various duty cycles; you can recognize these rather

easily just by inspection. Text explains calculations involved in more

critical duty-cycle measurements.

The relationship between logic-high time and logic-low time grows quite significant in certain applications. Your interest should be directed to how much to total time the signal stays logic-high. The timing in one complete high/low cycle can disclose this information.

In Figure 4A, the digital wave form is up for two divisions out of every three. That means logic is high two-thirds of the total time. Its duty cycle, therefore, could be expressed as the fraction 2/3.

Duty cycle also can express logic-high time as a percentage of total time in one high/low cycle.

For Figure 4A, divide the two divisions of high by the three total high/low divisions, and multiply the result by 100. The answer is 66.67% usually rounded to 67%.

Figure 4B portrays a digital signal with a different duty cycle.

Logic-high time covers two divisions; logic-low time takes up three. Total time for one high/low cycle is five divisions. Hence, the digital signal is logic-high for two out of five time units, whatever they might be. The scope's time base must be known to evaluate how much time each division represents. This is not necessary for computing duty cycle.) Duty cycle in Figure 4B amounts to two divided by five, giving a decimal of 0.4 and a duty cycle of 40%.

The digital signal in Figure 4C is logic-high for more time than it is logic-low. Logic-high uses up three of five time-units (graticule divisions). Divide three by five, and you establish that the cycle is 0.6 or 60%.

You should be able to calculate duty cycle in Figure 4D without assistance. Logic-high time is seven divisions; logic-low exists for a mere two divisions. What is the duty cycle? Your reasoning and calculations should run something like this:

Total time for one high/low cycle in this digital signal is nine divisions of the graticule. Of those nine time-segments, the logic-high condition prevails for seven. Hence, seven divided by nine equals 0.7778, which rounds off to a duty cycle of 0.78 or 78%.

DC reference for digital Now, think back to the steady state digital signals mentioned in the first paragraphs of this article.

Remember, they are merely DC voltages applied (for on or logic-high) or not applied (off or logic-low). Or, you can think of them as dc voltages (logic-high) or circuit grounds (logic-low). You can detect these steady-state digital signals three ways.

Simplest, if you have the instrument handy, is with a logic probe.

A light-emitting diode (LED) in the probe lights when logic is high at a point being tested, and stays dark when the point is at logic-low.

Some technicians prefer using a voltmeter. If the logic incorporates TTL-family devices (or DTL, RTL, or other TL configurations), the 10V scale of a voltmeter shows quickly whether a circuit point or terminal is logic-high (3V to 5V) or logic-low (near zero). For CMOS type logic, use the 20V or 30V scale to detect logic-high (around 14V) or logic-low (near zero).

For the sake of utility, technicians should master the third method, using a scope. While that might seem a bit elaborate, it really is not. Even with steady-state logic systems, troubles occur that cannot be revealed by logic probe or voltmeter.

Few technicians use their scopes for dc measurements. In situations where voltages may reach 100V or 200V dc, that's understandable; signal levels, by comparison, would be lost. But in digital-electronic systems, you can save considerable troubleshooting time if you accustom yourself to measuring dc voltages with your scope. Coincidentally, you can do a better job of signal analysis, even with steady state digital signals.

These methods are relatively simple. A few exercises will familiarize you with techniques used by experienced digital technicians.

Turn on your scope, and set it for automatic triggering. This delivers a trace, even without an input signal. If the scope is dual-trace, set it first to use one input channel only.

Set the scope's input mode for dc coupling. Continue to use the 10:1 probe. This is always a good idea during troubleshooting, unless the greater sensitivity of a direct probe is needed.

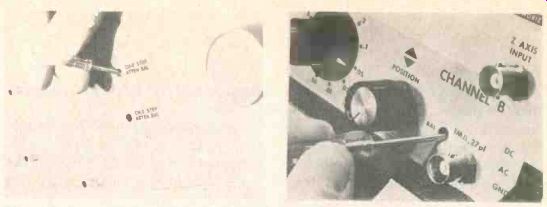

Clip the probe ground lead to its tip. This assures a definite zero volts or logic-low. Adjust the trace line on the scope screen to sweep along the centerline (Figure 5A).

This will constitute a zero-voltage reference or logic-low base line.

A flashlight battery offers a handy source of dc voltage for this introductory exercises. Hold the ground lead of the probe against the negative end of the battery, and touch the probe tip to the positive post. The whole trace moves upward.

Figure 5---With graticule centerline as zero-base, these displays show

dc measurements with scope on automatic triggering. Text exercises show

how to obtain these with your own scope.

Setting of the scope's input attenuator determines how far the trace deflects upward. Turn that switch to 0.05V/div (50mV/div on some scopes. For a direct probe, the 0.5V/div position is the same.) Figure 5B shows the result of measuring a fresh D-cell. Voltage applied to the probe has raised the trace three divisions plus one subdivision. Each Y-axis division represents 0.5V, and each subdivision equals 0.1V. Consequently, dc voltage measured by the scope in Fig. 5B is 1.6V.

Think of this in digital terms. A 1.6V steady-state high has been sensed by the dc input of the scope.

This deflects the trace-the whole trace-an amount proportional to its amplitude and to the sensitivity setting (input attenuator) of the scope.

Why the whole trace? Because time duration of the applied logic high exceeds the time base of the scope's sweep. The scope beam keeps tracing the same 1.6V path again and again. The DC high holds the trace at that level until you decide to take the voltage away by removing the probe tip from the D-cell post. Then the voltage drops back to the zero-reference base line established earlier. And it stays there as long as the probe senses a ground (no voltage).

Connect the scope next to a 9V transistor-radio battery, probe to positive and ground clip to negative. The trace deflects far off-screen. This means input sensitivity must be reduced. Flip the volts/div switch to higher and higher values until one is reached that provides on-screen deflection of the trace.

Figure 5C reveals a deflection of two full divisions. The input attenuator has been set at 0.5 volt/div, which represents 5 volts/div with a 10:1 probe in use. The battery used for Figure 5C must have been a fresh one; the dc value was almost 10V.

Possibly the most important fact to realize from these exercises is that the trace returns to the same zero-reference position every time the voltage is removed or the probe tip is grounded. Using the DC input mode of the scope, zero or logic-low always remains at the same reference line on the screen-which is established with the vertical-position knob. This holds true even when digital circuitry is switching high and low at very rapid rates, and for all sorts of pulse durations.

In Figure 6A, a TTL pulse signal has its zero-base along the second line below center on the graticule.

Signal highs happen to be at 4.5V.

They therefore fall between the second and third lines above center on the graticule.

Question: What setting has been chosen for the volts/div switch to make the display in Figure 6A? If you answered 0.1V/div, you're catching on-and you remembered to consider the 10:1 probe.

Using the same reasoning, figure out the proper input setting for the CMOS digital signal in Figure 6B. of its logic-high condition. You are right if you found logic-high to be 14V, and the attenuator set at 0.5V/div.

One final caution about scopes and the dc input mode. In some scope models, dc balance drifts quite a bit during warmup. Imbalance can alter the zero base as you switch attenuator ranges.

To combat balance errors, and for other good reasons, keep your scope on and warmed up all the time. If balance drift poses a problem after a 1-hour warmup, you might have to recalibrate dc balance in your scope every day or two-in both channels.

Short the probe tip to its ground lead. Find the dc-balance control for the active channel (see Figures 7A and 7B). While switching between 0.5, 0.2, and 0.1 on the volts/div dial, adjust DC balance (sometimes called attenuator balance) until the trace remains at the same place on the screen for all settings of the attenuator knob.

Check other positions too, and refine the dc balance adjustment as necessary. Repeat with the other channel.

Figure 7---Dc balance adjustments may be on front or on side of your

scope.

Short probe tip to ground, and adjust balance until trace stays at zero position at all input settings.

Figure 6---These are digital signals with pulses shorter in time than

logic-low times. (A) TTL signal with value of 4.5V. (B) CMOS uses higher

voltage, 14V in signal shown here.

Time base and triggering

In the Electronics Upgrading Seminars we conduct for LIAISON, one day is devoted to hands-on familiarization with triggered scopes. In those sessions, the following question comes up regularly:

What scope time base should be selected to make dc measurements? The answer will appear in the next article of this two-part series.

It will also include a step-by-step procedure for analyzing any digital signal very quickly.

Note: This two-article series has been adapted from a forthcoming Forest Belt's Service Training Monograph titled: "Triggered Oscilloscopes Waveforms and How to Analyze Them." Filled with waveform photographs and explanations, this new Monograph will function as both training guide and reference manual for analog and digital signals your triggered scope should find in a wide variety of modern electronic equipment.

You will see waveforms--good and bad--from television, industrial controls, communications gear, microprocessors, and the like.

Release of this third Monograph in the Forest Belt "Triggered Oscilloscopes" series is scheduled Or later this year. If you want to be advised when this new publication is ready for shipment, mail your name and address and the notation "68A-E1/280" to: Service Training Group, P.O. Box 47, West Newton. IN 46183 (no obligation). STG will send you an order form when the "Waveforms" Monograph has been printed.

Also see: SCR regulator and horizontal oscillator